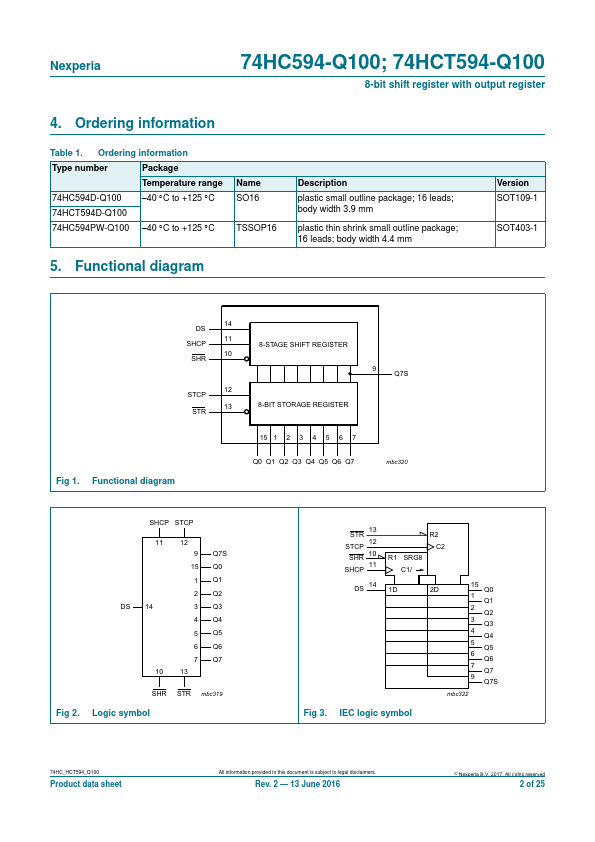

74HCT594-Q100 Description

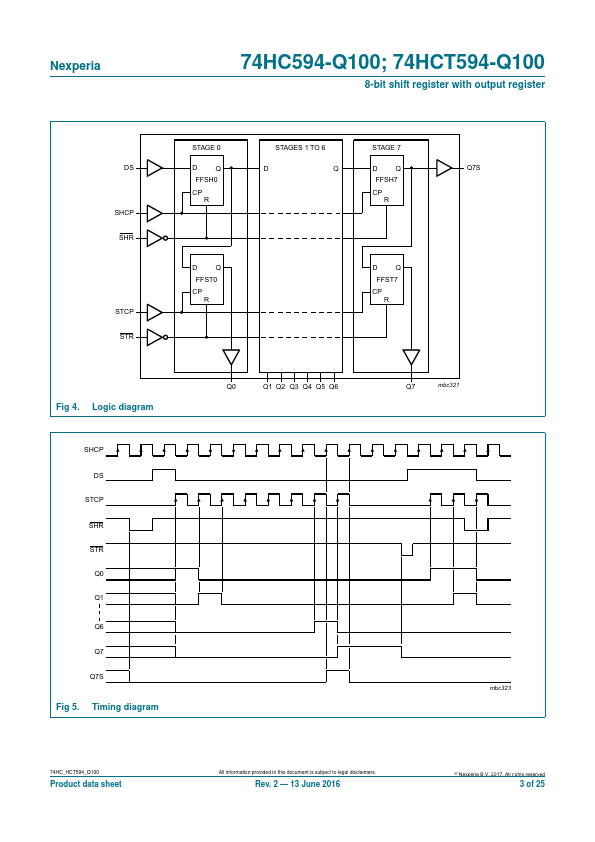

74HCT594-Q100 is a high-speed Si-gate CMOS device and is pin patible with Low-Power Schottky TTL (LSTTL). 74HCT594-Q100 is an 8-bit, non-inverting, serial-in, parallel-out shift register that feeds an 8-bit D-type storage register. Separate clocks (SHCP and STCP) and direct overriding clears (SHR and STR) are provided on both the shift and storage registers.

74HCT594-Q100 Key Features

- Automotive product qualification in accordance with AEC-Q100 (Grade 1)

- Specified from 40 C to +85 C and from 40 C to +125 C

- Synchronous serial input and output

- plies with JEDEC standard No.7A

- 8-bit parallel output

- Shift and storage registers have independent direct clear and clocks

- Independent clocks for shift and storage registers

- 100 MHz (typical)

- ESD protection

- MIL-STD-883, method 3015 exceeds 2000 V

74HCT594-Q100 Applications

- Automotive product qualification in accordance with AEC-Q100 (Grade 1) Specified from 40 C to +85 C and from 40 C to +125 C