74LVC2G74 Description

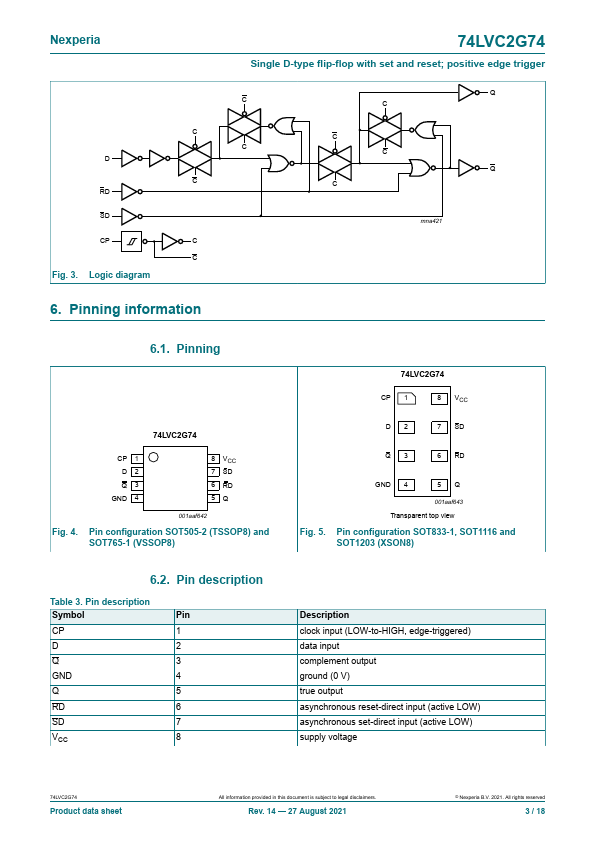

The 74LVC2G74 is a single positive edge triggered D-type flip-flop with individual data (D), clock (CP), set (SD) and reset (RD) inputs, and plementary Q and Q outputs. Data at the D-input that meets the set-up and hold time requirements on the LOW-to-HIGH clock transition will be stored in the flip-flop and appear at the Q output. Inputs can be driven from either 3.3 V or 5 V devices.

74LVC2G74 Key Features

- Wide supply voltage range from 1.65 V to 5.5 V

- Overvoltage tolerant inputs to 5.5 V

- High noise immunity

- plies with JEDEC standard

- JESD8-7 (1.65 V to 1.95 V)

- JESD8-5 (2.3 V to 2.7 V)

- JESD8-B/JESD36 (2.7 V to 3.6 V)

- ±24 mA output drive (VCC = 3.0 V)

- ESD protection

- HBM JESD22-A114F exceeds 2000 V

74LVC2G74 Applications

- Wide supply voltage range from 1.65 V to 5.5 V

- Overvoltage tolerant inputs to 5.5 V