Datasheet Summary

HEF4543B

BCD to 7-segment latch/decoder/driver

Rev. 9

- 15 August 2024

Product data sheet

1. General description

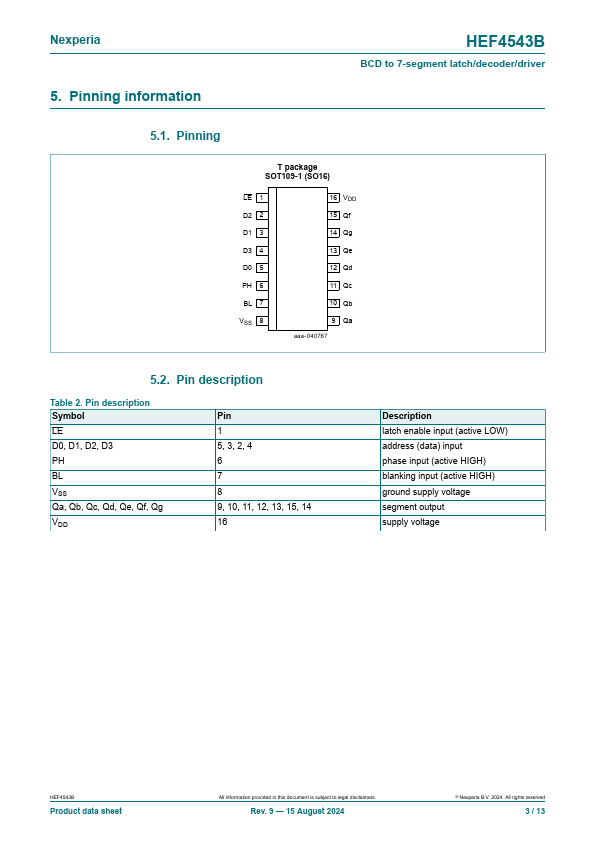

The HEF4543B is a BCD to 7-segment latch/decoder/driver for liquid crystal and LED displays. It has four address inputs (D0 to D3), an active LOW latch enable input (LE), an active HIGH blanking input (BL), an active HIGH phase input (PH) and seven buffered segment outputs (Qa to Qg).

The circuit provides the function of a 4-bit storage latch and an 8-4-2-1 BCD to 7-segment decoder/driver. It can invert the logic levels of the output bination. The phase (PH), blanking (BL) and latch enable (LE) inputs are used to reverse the function table phase, blank the display and store...