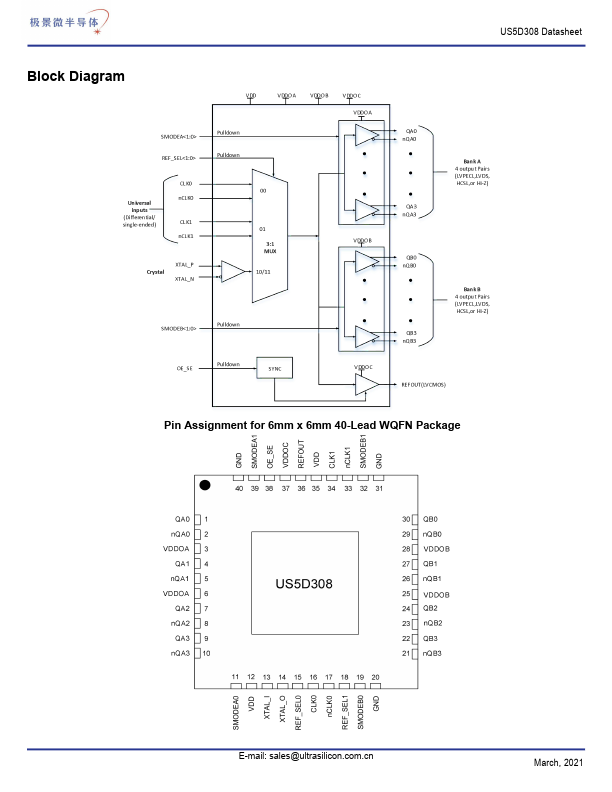

US5D308 Key Features

- Two differential reference clock input pairs

- Differential input pairs can accept the following differential input

- Crystal Input accepts 10MHz to 40MHz Crystal or Single Ended

- Maximum Output Frequency

- 2.1GHz LVDS

- 2.1GHz HCSL

- 250MHz LVCMOS

- 250MHz

- Two banks, each has four differential output pairs that can be

- Output skew: 20ps (typical)