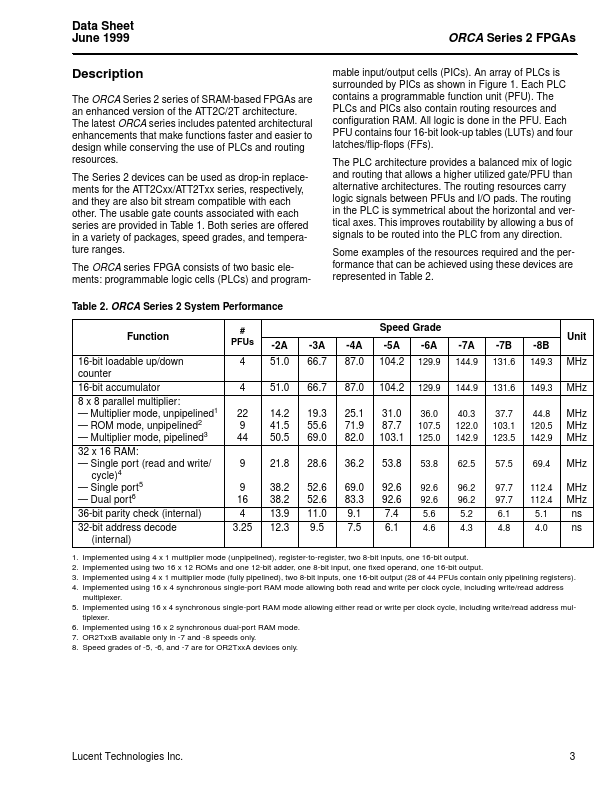

Description

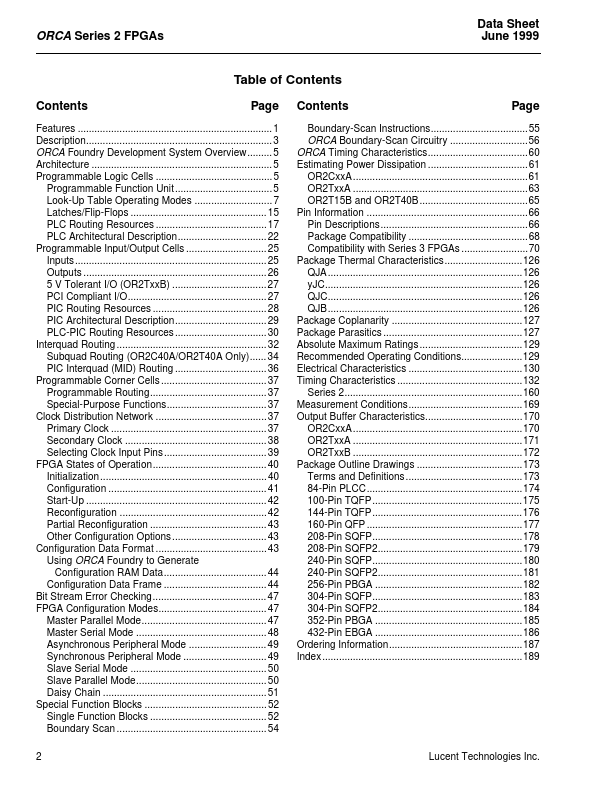

3 ORCA Foundry Development System Overview 5 Architecture 5 Programmable Logic Cells 5 Programmable Function Unit 5 Look-Up Table Operating Modes 7 Latches/Flip-Flops 15 PLC Routing Resources 17 PLC Architectural Description 22 Programmable Input/Output Cells 25 Inputs 25 Outputs 26 5 V Tolerant I/O (OR2TxxB) 27 PCI Compliant I/O 27 PIC Routing Resources 28 PIC Architectural Description 29 PLC-PIC Routing Resources 30 Interquad Routing 32 Subquad Routing (OR2C40A/OR2T40A Only) 34 PI

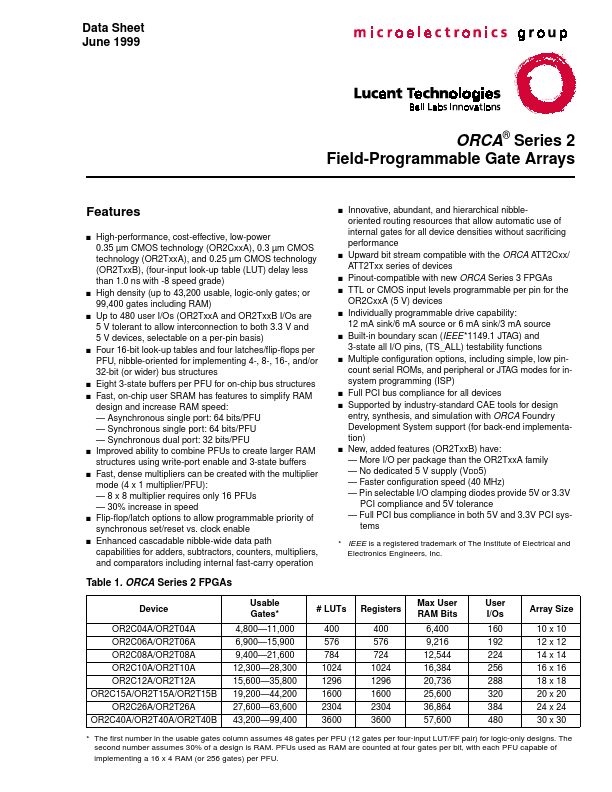

Features

- s

s

s

s

s

s s

s

s

s

s

High-performance, cost-effective, low-power 0.35 µm CMOS technology (OR2CxxA), 0.3 µm CMOS technology (OR2TxxA), and 0.25 µm CMOS technology (OR2TxxB), (four-input look-up table (LUT) delay less than 1.0 ns with -8 speed grade) High density (up to 43,200 usable, logic-only gates; or 99,400 gates including RAM) Up to 480 user I/Os (OR2TxxA and OR2TxxB I/Os are 5 V tolerant to allow interconnection to both 3.3 V and 5 V devices, selectable on a per-pin basis) Four 1.