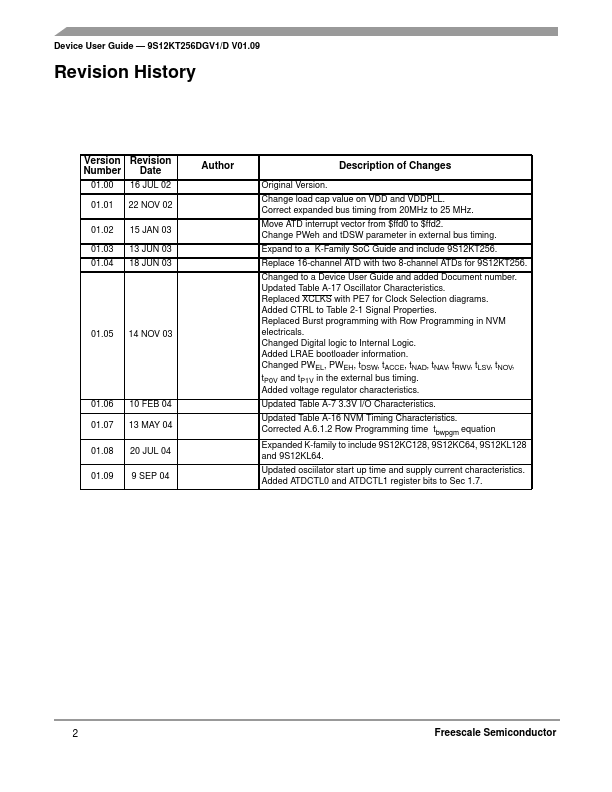

Description

of Changes

Change load cap value on VDD and VDDPLL.Correct expanded bus timing from 20MHz to 25 MHz.Move ATD interrupt vector from $ffd0 to $ffd2. Change PWeh and tDSW parameter in external bus timing.Expand to a K-Family SoC Guide and include 9S12KT256. Replace 16-channel ATD with two 8-channel ATDs for 9S12KT256. Changed to a Device User Guide and added Document number.Updated Table A-17 Oscillator Characteristics.Replaced XCLKS with PE7 for Clock Selection diagrams.Added CTRL to Table 2

Features

- . . . 15 Modes of Operation.

- . . . . 17 MC9S12KG(L)(C)128(64)(32) Block Diagram.

- . . . . 19 MC9S12KT(G)256 Block Diagram.

- . . . 20 Device Memory Map.