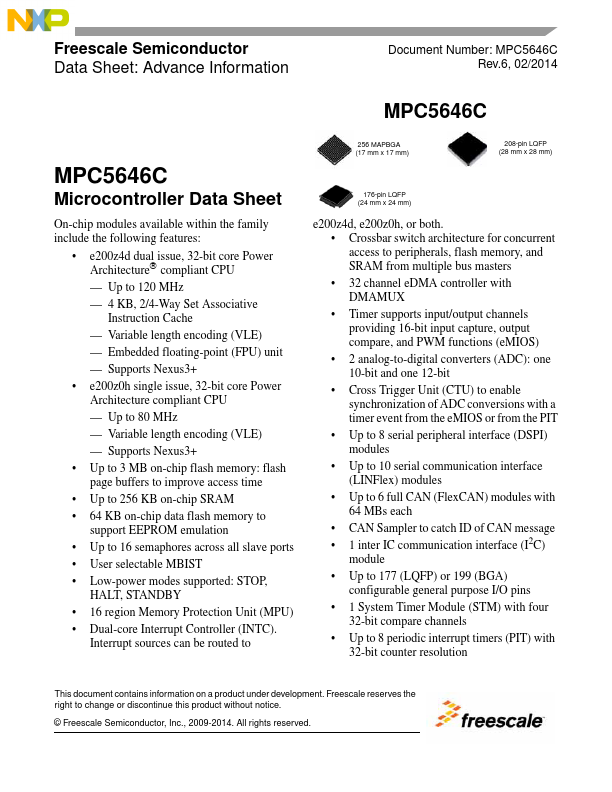

MPC5646C

Key Features

- e200z0h single issue, 32-bit core Power Architecture pliant CPU — Up to 80 MHz — Variable length encoding (VLE) — Supports Nexus3+

- Up to 3 MB on-chip flash memory: flash page buffers to improve access time

- Up to 256 KB on-chip SRAM

- 64 KB on-chip data flash memory to

- Up to 16 semaphores across all slave ports

- User selectable MBIST

- Low-power modes supported: STOP

- 16 region Memory Protection Unit (MPU)

- Dual-core Interrupt Controller (INTC)