Description

Table

Symbol

Description

Type Comments

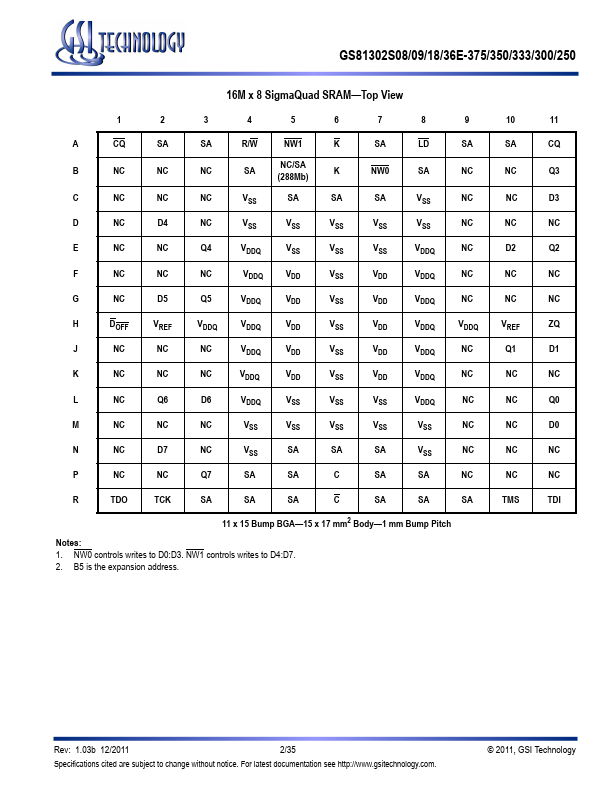

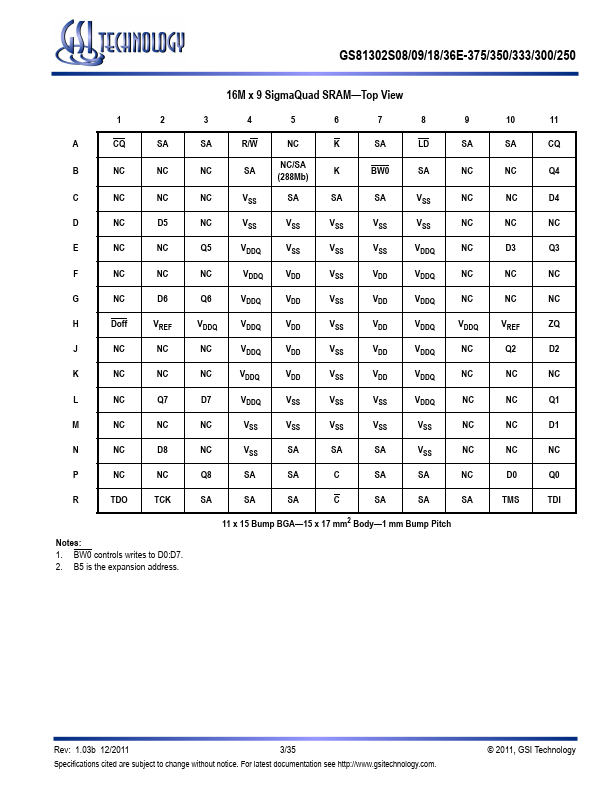

SA

Synchronous Address Inputs

Input

R/W

Read/Write Contol Pin

Input Write Active Low; Read Active High

NW0

NW1

Synchronous Nybble Writes

Input

Active Low x08 Version

BW0

BW1

Synchronous Byte Writes

Input

Active Low x18 Version

BW0

BW3

Synchronous Byte Writes

Input

Active Low x36 Version

K

Input Clock

Input Active High

C

Output Clock

Input Active High

TMS

Test Mode Select

Input

TDI

T

Features

- Simultaneous Read and Write SigmaSIO™ Interface.

- JEDEC-standard pinout and package.

- Dual Double Data Rate interface.

- Byte Write controls sampled at data-in time.

- DLL circuitry for wide output data valid window and future

frequency scaling.

- Burst of 2 Read and Write.

- 1.8 V +100/.

- 100 mV core power supply.

- 1.5 V or 1.8 V HSTL Interface.

- Pipelined read operation.

- Fully coherent read and write pipelines.