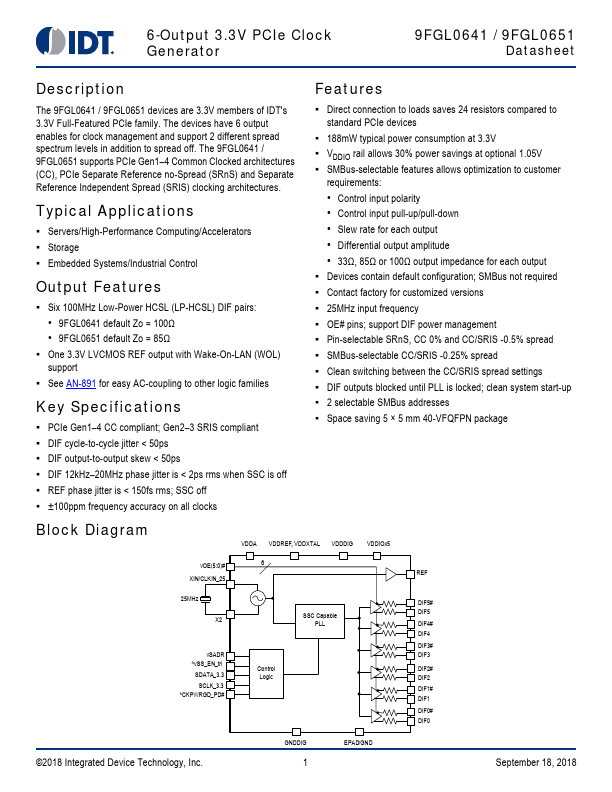

Description

The 9FGL0641 / 9FGL0651 devices are 3.3V members of IDT's 3.3V Full-Featured PCIe family.

4 Common Clocked architectures (CC), PCIe Separate Reference no-Spread (SRnS) and Separate Reference Independent Spread (SRIS) clocking architectures.

Servers/High-Performance Computing/Accelerators

Features

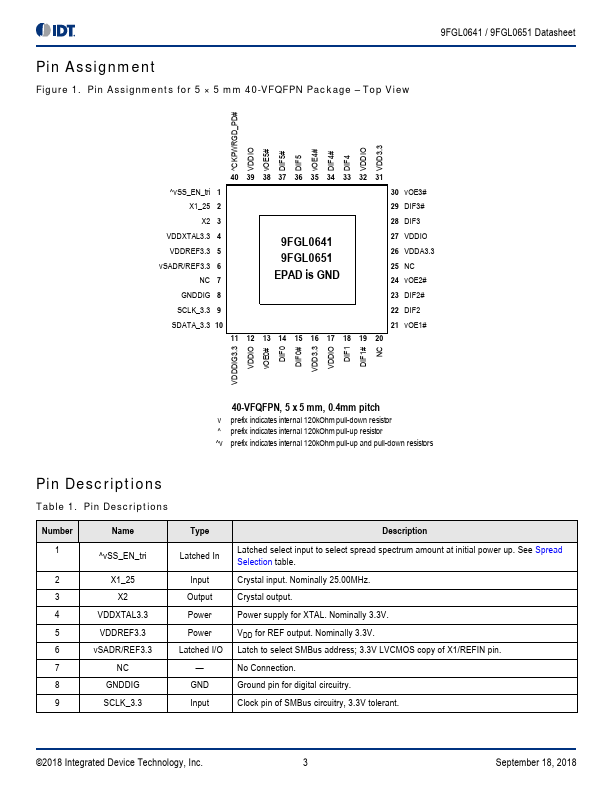

- Six 100MHz Low-Power HCSL (LP-HCSL) DIF pairs:.

- 9FGL0641 default Zo = 100Ω.

- 9FGL0651 default Zo = 85Ω.

- One 3.3V LVCMOS REF output with Wake-On-LAN (WOL) support.

- See AN-891 for easy AC-coupling to other logic families

Key Specifications.

- PCIe Gen1.

- 4 CC compliant; Gen2.

- 3 SRIS compliant.

- DIF cycle-to-cycle jitter < 50ps.

- DIF output-.