SY100EL14V

Description

The SY100EL14V is a low-skew, 1:5 clock distribution chip designed explicitly for low-skew clock distribution applications. The device can be driven by either a differential or single-ended ECL or, if positive power supplies are used, PECL input signal. The EL14V is suitable for operation in systems operating with 3.3V to 5.0V supplies. If a single-ended input is to be used, the VBB output should be connected to the /CLK input and bypassed to ground via a 0.01µF capacitor. The VBB output is designed to act as the switching reference for the input of the EL14V under single-ended input conditions. As a result, this pin can only source/sink up to 0.5m A of current.

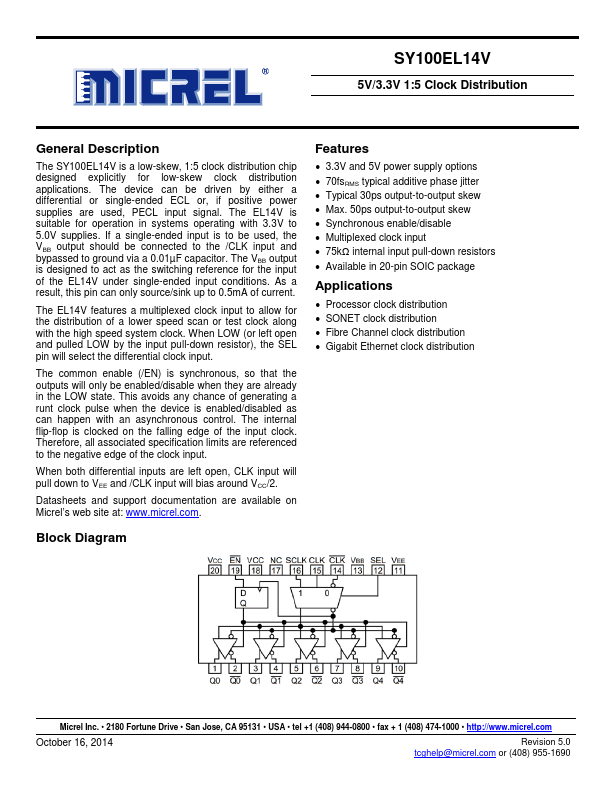

The EL14V features a multiplexed clock input to allow for the distribution of a lower speed scan or test clock along with the high speed system clock. When LOW (or left open and pulled LOW by the input pull-down resistor), the SEL pin will select the differential clock input.

The mon enable (/EN) is synchronous, so...