SY100EL15L Overview

Description

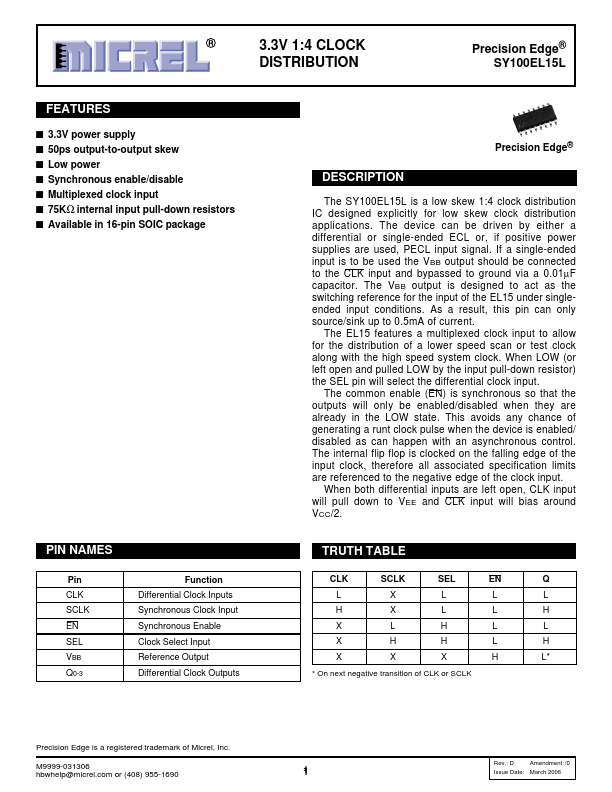

The SY100EL15L is a low skew 1:4 clock distribution IC designed explicitly for low skew clock distribution applications. The device can be driven by either a differential or single-ended ECL or, if positive power supplies are used, PECL input signal.