SY100EL14V Overview

Description

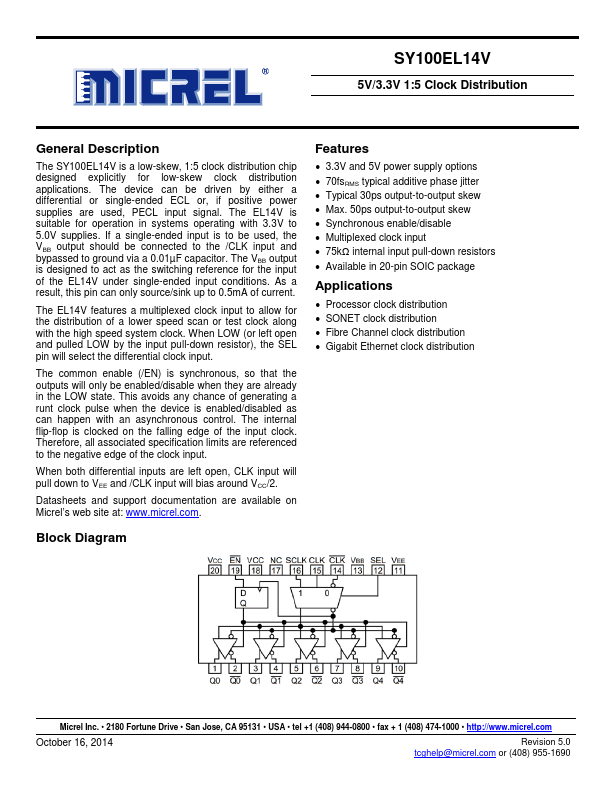

The SY100EL14V is a low-skew, 1:5 clock distribution chip designed explicitly for low-skew clock distribution applications. The device can be driven by either a differential or single-ended ECL or, if positive power supplies are used, PECL input signal.

Key Features

- 3.3V and 5V power supply options

- 70fsRMS typical additive phase jitter

- Typical 30ps output-to-output skew

- Max. 50ps output-to-output skew

- Synchronous enable/disable

- Multiplexed clock input

- 75kΩ internal input pull-down resistors

- Available in 20-pin SOIC package