Description

7

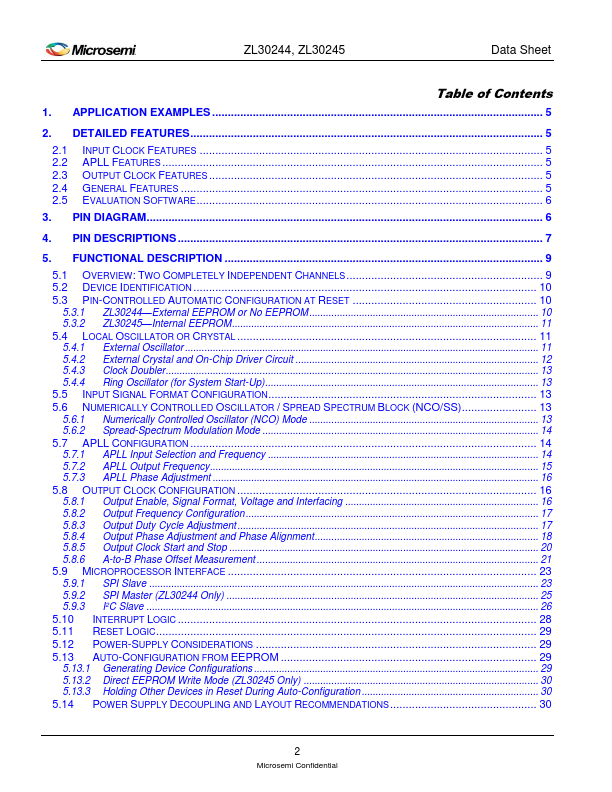

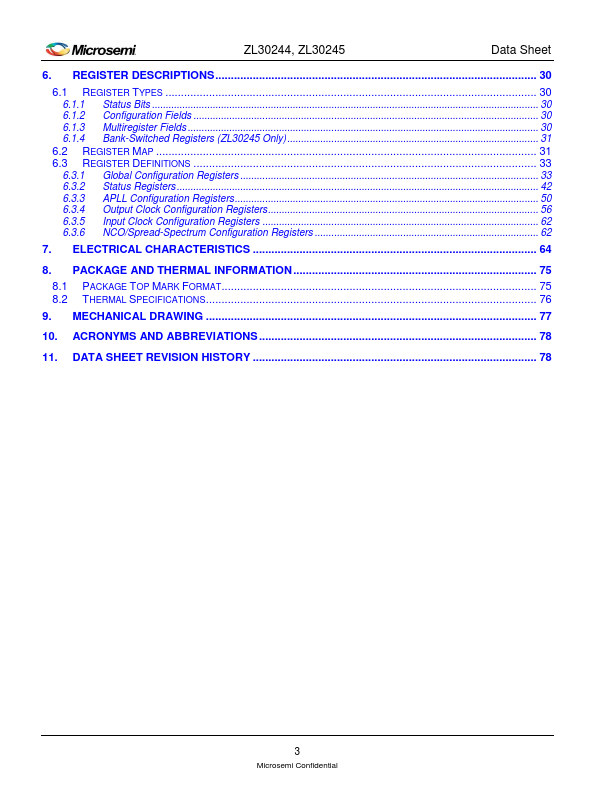

5. FUNCTIONAL DESCRIPTION 9

5.1 OVERVIEW: TWO COMPLETELY INDEPENDENT CHANNELS 9 5.2 DEVICE IDENTIFICATION 10 5.3 PIN-CONTROLLED AUTOMATIC CONFIGURATION AT RESET 10

5.3.1 ZL30244

External EEPROM or No EEPROM 10 5.3.2 ZL30245

Internal EEPROM 11

5.4 LOCAL OSCILLATOR OR CRYSTAL 11

5.4.1 External Oscillator 11 5.4.2 External Crystal and On-Chip Driver Circuit 12 5.4.3 Clock Doubler

Features

- Two Independent APLL Channels.

- Four Input Clocks Per Channel.

- One crystal/CMOS input.

- Two differential/CMOS inputs.

- One single-ended/CMOS input.

- Any input frequency from 9.72MHz to 1250MHz

(9.72MHz to 300MHz for CMOS).

- Clock selection by pin or register control.

- Low-Jitter Fractional-N APLL and 3 Outputs Per Channel.

- Any output frequency from.