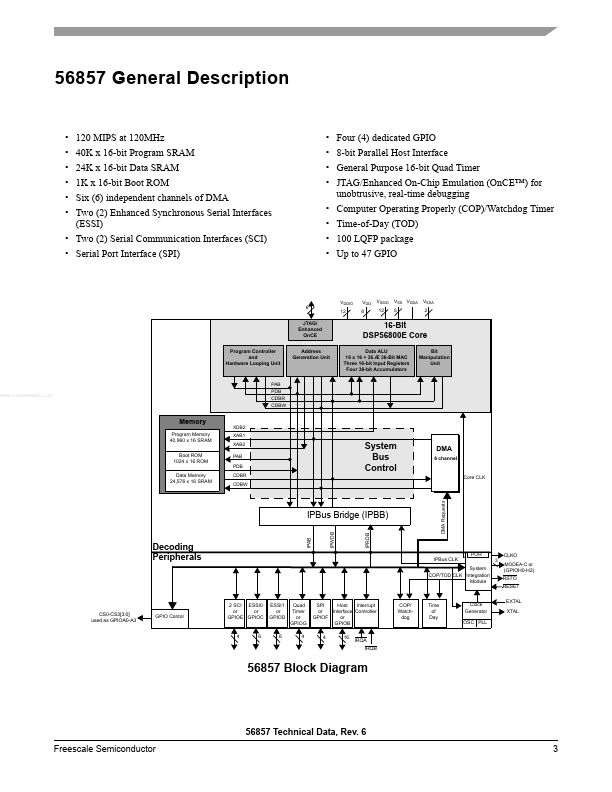

Description

120 MIPS at 120MHz

40K x 16-bit Program SRAM

24K x 16-bit Data SRAM

1K x 16-bit Boot ROM

Six (6) independent channels of DMA

Two (2) Enhanced Synchronous Serial Interfaces (ESSI)

Two (2) Serial Communication Interfaces (SCI)

Serial Port Interface (SPI)

Four (4) dedicated GPIO

8-bit Parallel Host Interface

General Purpose 16-bit Quad Timer

JTAG/Enhanced On-Chip Emulation (OnCE™)

Features

- 1.1.1.

- Digital Signal Processing Core

Efficient 16-bit engine with dual Harvard architecture 120 Million Instructions Per Second (MIPS) at 120MHz core frequency Single-cycle 16 × 16-bit parallel Multiplier-Accumulator (MAC) Four (4) 36-bit accumulators including extension bits 16-bit bidirectional shifter Parallel instruction set with uni.