74LS379

features the mon Enable rather then mon Master Reset.

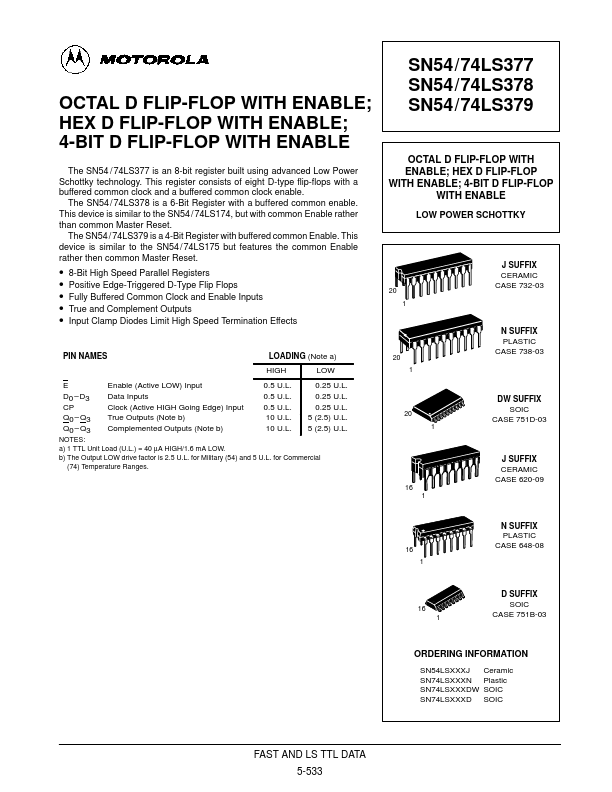

SN54/74LS377 SN54/74LS378 SN54/74LS379

OCTAL D FLIP-FLOP WITH ENABLE; HEX D FLIP-FLOP WITH ENABLE; 4-BIT D FLIP-FLOP WITH ENABLE

LOW POWER SCHOTTKY

- -

- -

- 8-Bit High Speed Parallel Registers Positive Edge-Triggered D-Type Flip Flops Fully Buffered mon Clock and Enable Inputs True and plement Outputs Input Clamp Diodes Limit High Speed Termination Effects

20 1

J SUFFIX CERAMIC CASE 732-03

PIN NAMES

LOADING (Note a) HIGH LOW 0.25 U.L. 0.25 U.L. 0.25 U.L. 5 (2.5) U.L. 5 (2.5) U.L.

20 1

N SUFFIX PLASTIC CASE 738-03

E D0

- D3 CP Q0

- Q3 Q0

- Q3

Enable (Active LOW) Input Data Inputs Clock (Active HIGH Going Edge) Input True Outputs (Note b) plemented Outputs (Note b)

0.5 U.L. 0.5 U.L. 0.5 U.L. 10 U.L. 10 U.L.

20 1

DW SUFFIX SOIC CASE 751D-03

NOTES: a) 1 TTL Unit Load (U.L.) = 40 µA HIGH/1.6 m A LOW. b) The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for mercial (74) Temperature Ranges. 16 1

J SUFFIX...