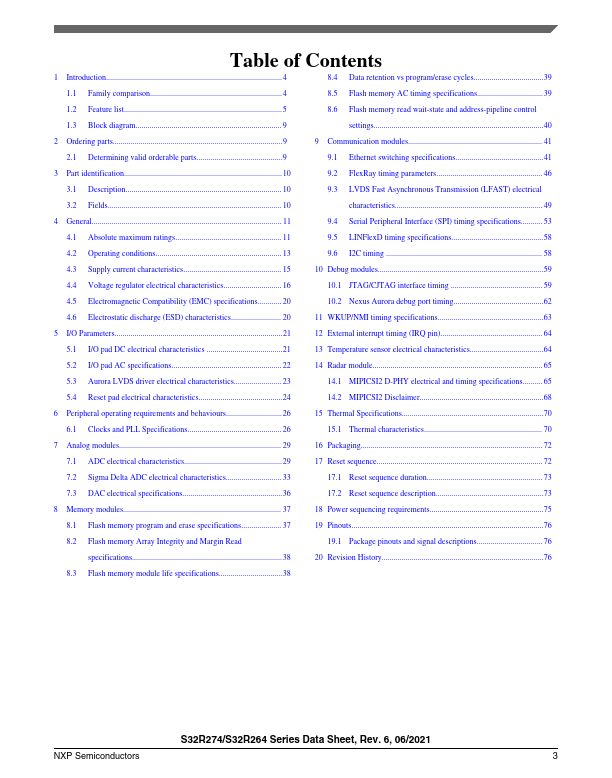

Description

10

9.3 LVDS Fast Asynchronous Transmission (LFAST) electrical

3.2 Fields 10

characteristics 49

4 General 11

9.4 Serial Peripheral Interface (SPI) timing specifications 53

4.1 Absolute maximum ratings 11

9.5 LINFlexD timing specifications

Features

- On-chip modules available within the device include the following features:.

- Safety core: Power Architecture® e200Z4 32-bit CPU with checker core.

- Dual issue computation cores: Power Architecture® e200Z7 32-bit CPU.

- 2 MB on-chip code flash (FMC flash) with ECC.

- 1.5 MB on-chip SRAM with ECC.

- RADAR processing.

- Signal Processing Toolbox (SPT) for RADAR signal processing acceleration.

- Cross Timing Engine (CTE) for precise timin.