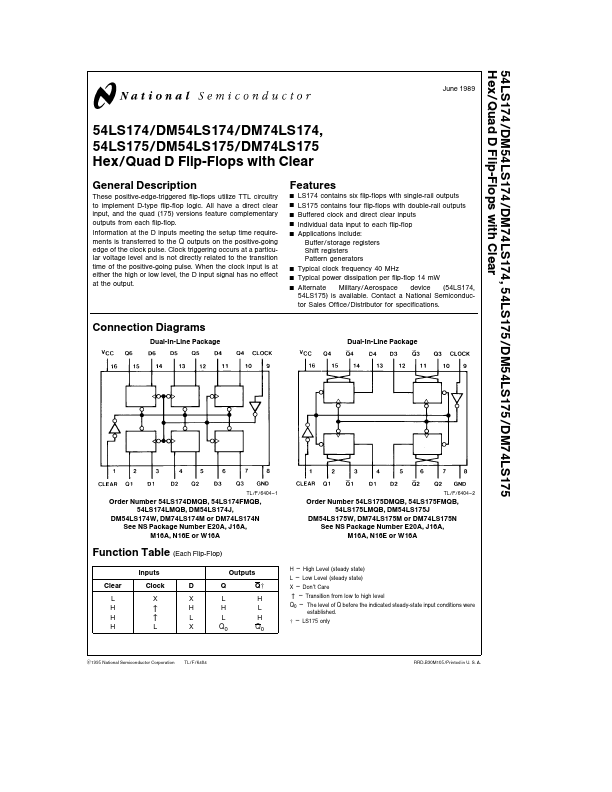

Description

These positive-edge-triggered flip-flops utilize TTL circuitry to implement D-type flip-flop logic All have a direct clear input and the quad (175) versions feature complementary outputs from each flip-flop

Information at the D inputs meeting the setup time requirements is transferred to the Q outputs on the positive-going edge of the clock pulse Clock triggering occurs at a particular voltage level and is not directly related to the transition time of the positive-going pulse When the clock inp

Features

- Y LS174 contains six flip-flops with single-rail outputs Y LS175 contains four flip-flops with double-rail outputs Y Buffered clock and direct clear inputs Y Individual data input to each flip-flop Y.