Description

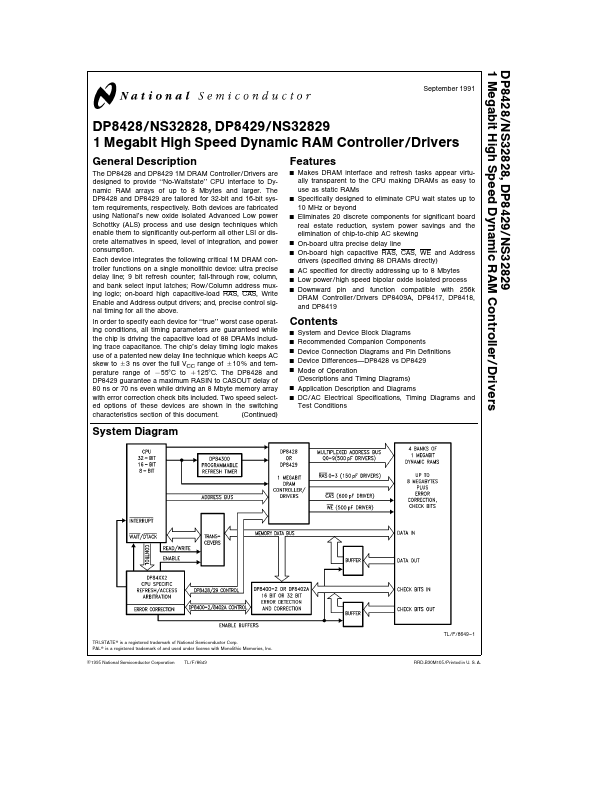

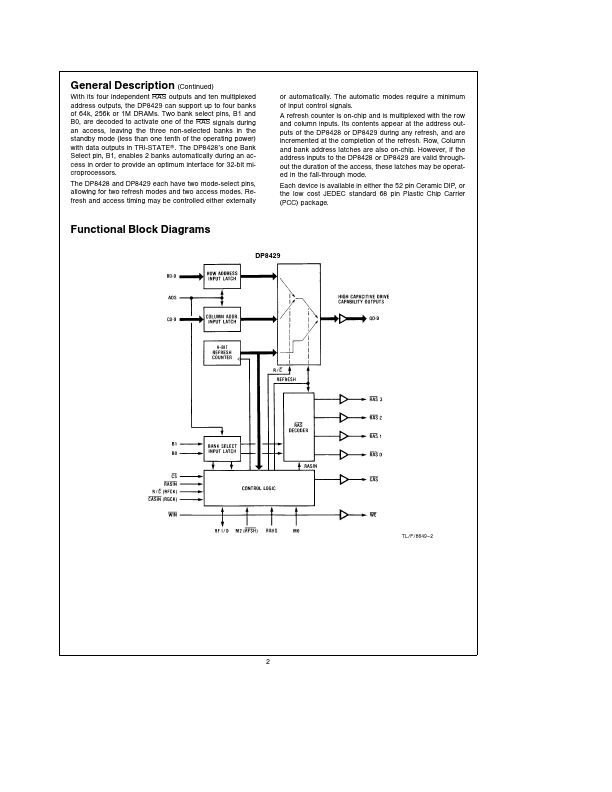

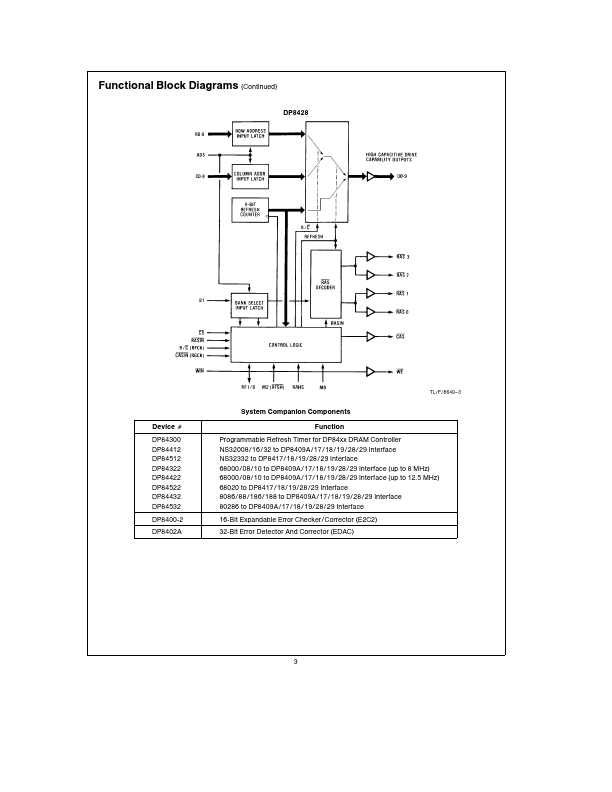

The DP8428 and DP8429 1M DRAM Controller Drivers are designed to provide ‘‘No-Waitstate’’ CPU interface to Dynamic RAM arrays of up to 8 Mbytes and larger The DP8428 and DP8429 are tailored for 32-bit and 16-bit system requirements respectively Both devices are fabricated using National’s new oxide isolated Advanced Low power Schottky (ALS) process and use design techniques which enable them to significantly out-perform all other LSI or discrete alternatives in speed level of integration and pow

Features

- Y

Y

Y

Y Y

Y Y Y

Makes DRAM interface and refresh tasks appear virtually transparent to the CPU making DRAMs as easy to use as static RAMs Specifically designed to eliminate CPU wait states up to 10 MHz or beyond Eliminates 20 discrete components for significant board real estate reduction system power savings and the elimination of chip-to-chip AC skewing On-board ultra precise delay line On-board high capacitive RAS CAS WE and Address drivers (specified driving 88 DRAMs directly) AC specif.