Description

1-1

2 system level description

2-1

2.1 overview

2-1

2.2 architecture

2-1

2.3 I/O control

2-4

2.4 format and frame rate

2-4

2.5 MIPI interface

2-4

2.6 power management

2.7 power up sequence

C 2.7.1 on-chip power up

2.8 power down sequence

o 2.9 system clock control n 2.10 SCCB interface T f 2.11 group write I i 3 block level description A d 3.1 pixel array structure N e 3.2 2x2 binning n 3.3 analog amplifier Q t 3.4 10-bit A/D converters I i 4 image sensor core digital functions N

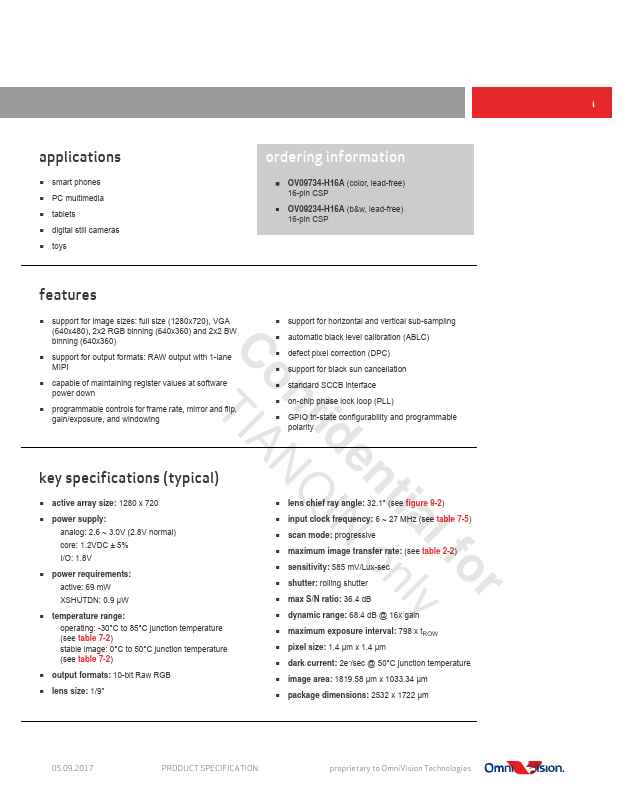

Features

- support for image sizes: full size (1280x720), VGA (640x480), 2x2 RGB binning (640x360) and 2x2 BW binning (640x360)

C support for output formats: RAW output with 1-lane

MIPI

o capable of maintaining register values at software n power down

programmable controls for frame rate, mirror and flip,

TI fi gain/exposure, and windowing

support for horizontal and vertical sub-sampling automatic black level calibration (ABLC) defect pixel correction (DPC) support for black sun cancellation standard SCC.