Description

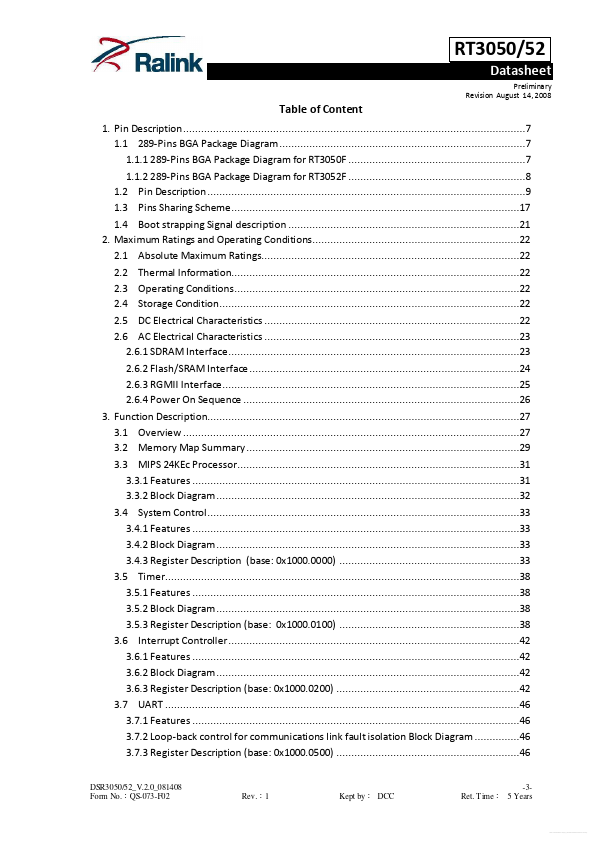

7 1.1 289-Pins BGA Package Diagram 7 1.1.1 289-Pins BGA Package Diagram for RT3050F 7 1.1.2 289-Pins BGA Package Diagram for RT3052F 8 1.2 Pin Description 9 1.3 Pins Sharing Scheme 17 1.4 Boot strapping Signal description 21 2.

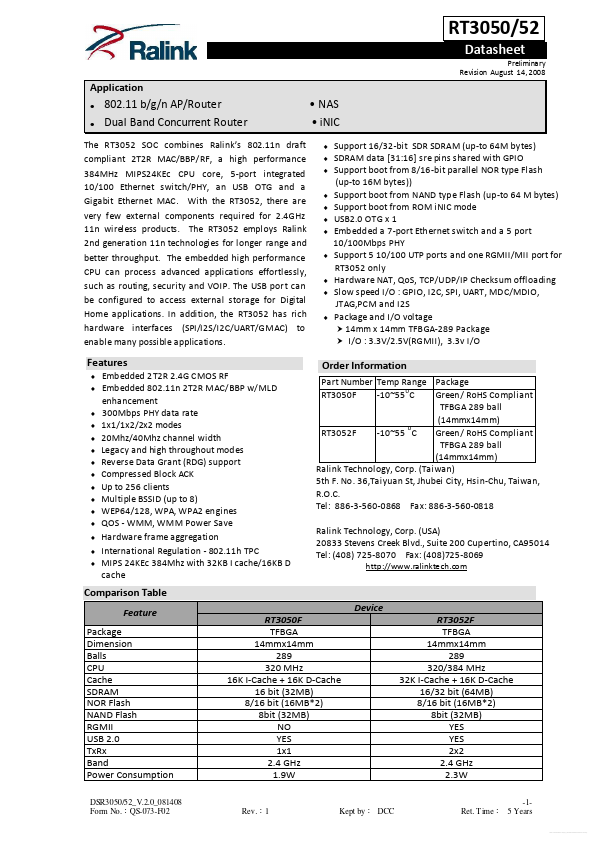

Features

- Embedded 2 T2R 2.4G CMOS RF Embedded 802.11n 2T2R MAC/BBP w/MLD

Order Information

Part Number Temp Range Package 0 RT3050F -10~55 C Green/ RoHS Compliant TFBGA 289 ball (14mmx14mm) 0 RT3052F -10~55 C Green/ RoHS Compliant TFBGA 289 ball (14mmx14mm) Ralink Technology, Corp. (Taiwan) 5th F. No. 36,Taiyuan St, Jhubei City, Hsin-Chu, Taiwan, R. O. C. Tel: 886-3-560-0868 Fax: 886-3-560-0818 Ralink Technology, Corp. (USA) 20833 Stevens Creek Blvd. , Suite 200 Cupertino, CA95014 Tel: (408) 725-8070 F.