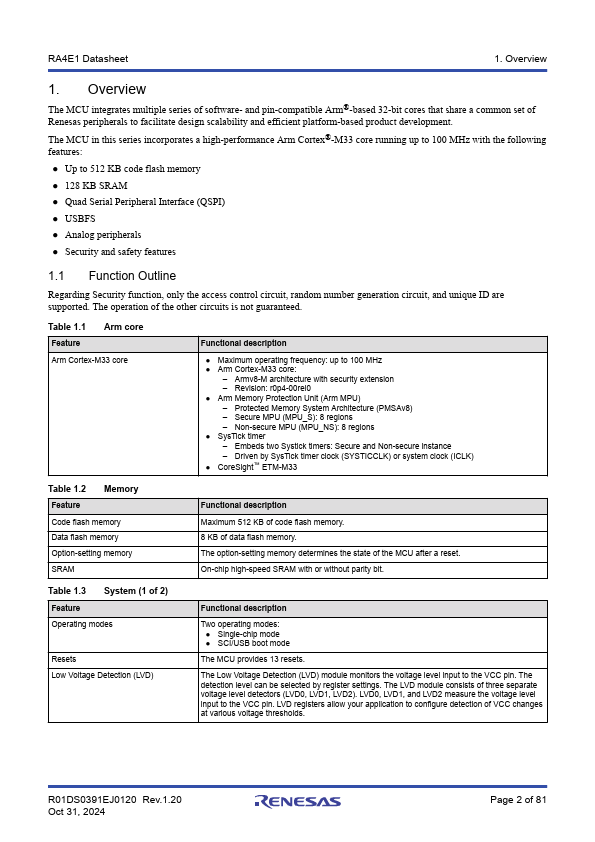

Description

Maximum operating frequency: up to 100 MHz

Arm Cortex-M33 core:

Armv8-M architecture with security extension

Revision: r0p4-00rel0

Arm Memory Protection Unit (Arm MPU)

Protected Memory System Architecture (PMSAv8)

Secure MPU (MPU_S): 8 regions

Non-secure MPU (MPU_NS): 8 regions

SysTick timer

Embeds two Systick timers: Secure and Non-secure instance

Driven by SysTick timer clock (SYSTICCLK) or system clo

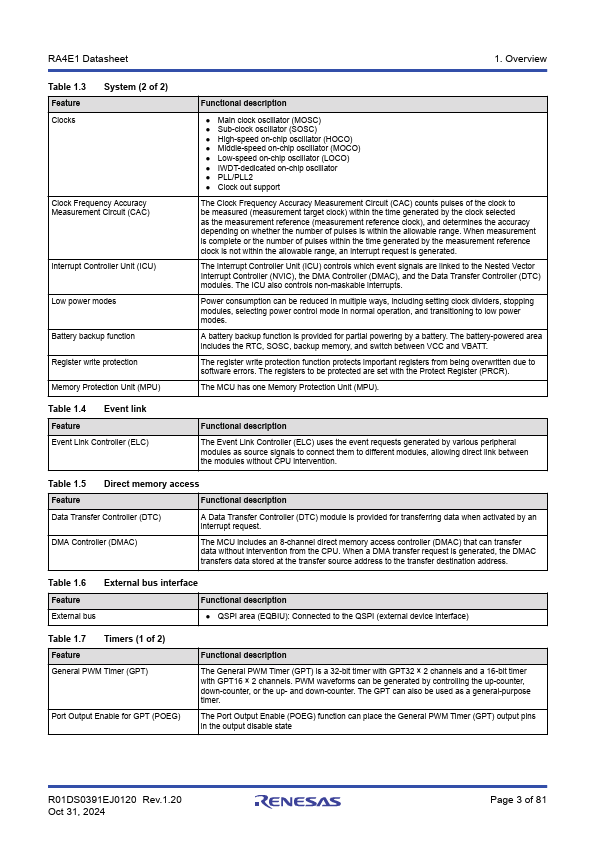

Features

- Arm® Cortex®-M33 Core.

- Armv8-M architecture with the main extension.

- Maximum operating frequency: 100 MHz.

- Arm Memory Protection Unit (Arm MPU).

- Protected Memory System Architecture (PMSAv8).

- Secure MPU (MPU_S): 8 regions.

- Non-secure MPU (MPU_NS): 8 regions.

- SysTick timer.

- Embeds two Systick timers: Secure and Non-secure instance.

- Driven by LOCO or system clock.

- CoreSight™ ETM-M33.

- Memory.

- Up to 512-KB code fl.