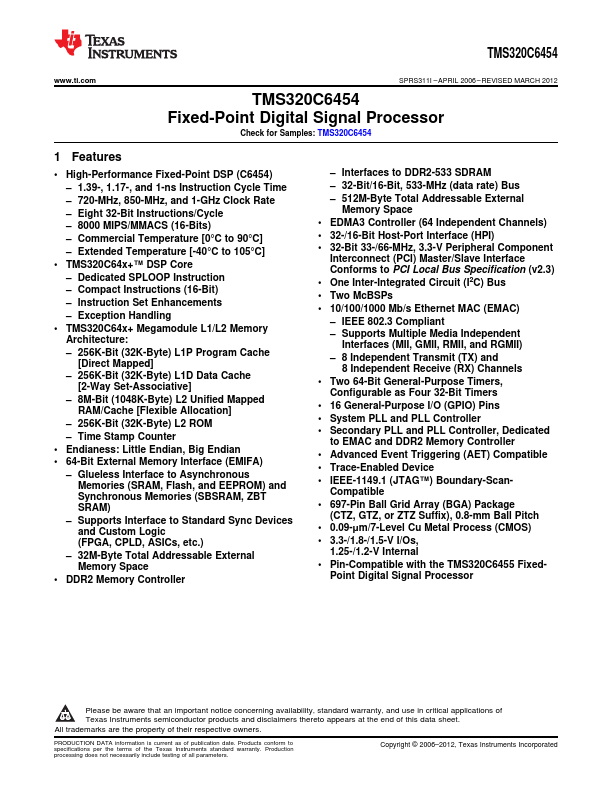

TMS320C6454

Overview

- High-Performance Fixed-Point DSP (C6454) - 1.39-, 1.17-, and 1-ns Instruction Cycle Time - 720-MHz, 850-MHz, and 1-GHz Clock Rate - Eight 32-Bit Instructions/Cycle - 8000 MIPS/MMACS (16-Bits) - Commercial Temperature [0°C to 90°C] - Extended Temperature [-40°C to 105°C]

- TMS320C64x+™ DSP Core - Dedicated SPLOOP Instruction - Compact Instructions (16-Bit) - Instruction Set Enhancements - Exception Handling

- TMS320C64x+ Megamodule L1/L2 Memory Architecture: - 256K-Bit (32K-Byte) L1P Program Cache [Direct Mapped] - 256K-Bit (32K-Byte) L1D Data Cache [2-Way Set-Associative] - 8M-Bit (1048K-Byte) L2 Unified Mapped RAM/Cache [Flexible Allocation] - 256K-Bit (32K-Byte) L2 ROM - Time Stamp Counter

- Endianess: Little Endian, Big Endian

- 64-Bit External Memory Interface (EMIFA) - Glueless Interface to Asynchronous Memories (SRAM, Flash, and EEPROM) and Synchronous Memories (SBSRAM, ZBT SRAM) - Supports Interface to Standard Sync Devices and Custom Logic (FPGA, CPLD, ASICs, etc.) - 32M-Byte Total Addressable External Memory Space

- DDR2 Memory Controller - Interfaces to DDR2-533 SDRAM - 32-Bit/16-Bit, 533-MHz (data rate) Bus - 512M-Byte Total Addressable External Memory Space

- EDMA3 Controller (64 Independent Channels)

- 32-/16-Bit Host-Port Interface (HPI)

- 32-Bit 33-/66-MHz, 3.3-V Peripheral Component Interconnect (PCI) Master/Slave Interface Conforms to PCI Local Bus Specification (v2.3)

- One Inter-Integrated Circuit (I2C) Bus