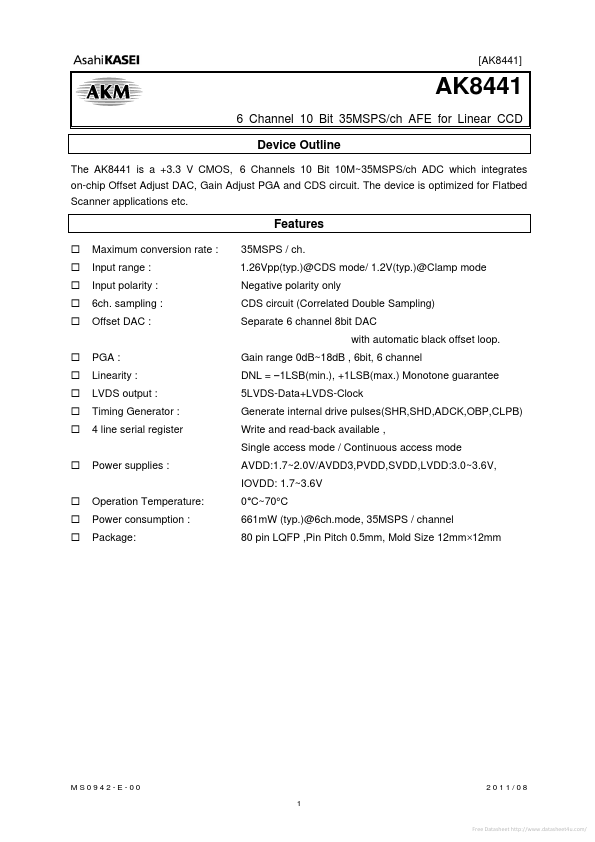

AK8441

AK8441 is 6 Channel 10 Bit 35MSPS/ch AFE manufactured by Asahi Kasei Microdevices.

[AK8441]

6 Channel 10 Bit 35MSPS/ch AFE for Linear CCD Device Outline

The AK8441 is a +3.3 V CMOS, 6 Channels 10 Bit 10M~35MSPS/ch ADC which integrates on-chip Offset Adjust DAC, Gain Adjust PGA and CDS circuit. The device is optimized for Flatbed Scanner applications etc.

Features

Maximum conversion rate : Input range : Input polarity : 6ch. sampling : Offset DAC : 35MSPS / ch. 1.26Vpp(typ.)@CDS mode/ 1.2V(typ.)@Clamp mode Negative polarity only CDS circuit (Correlated Double Sampling) Separate 6 channel 8bit DAC with automatic black offset loop. PGA : Linearity : LVDS output : Timing Generator : 4 line serial register Gain range 0dB~18dB , 6bit, 6...