S2052 Overview

Key Specifications

Package: SMD/SMT

Mount Type: Surface Mount

Pins: 6

Height: 8.75 mm

Description

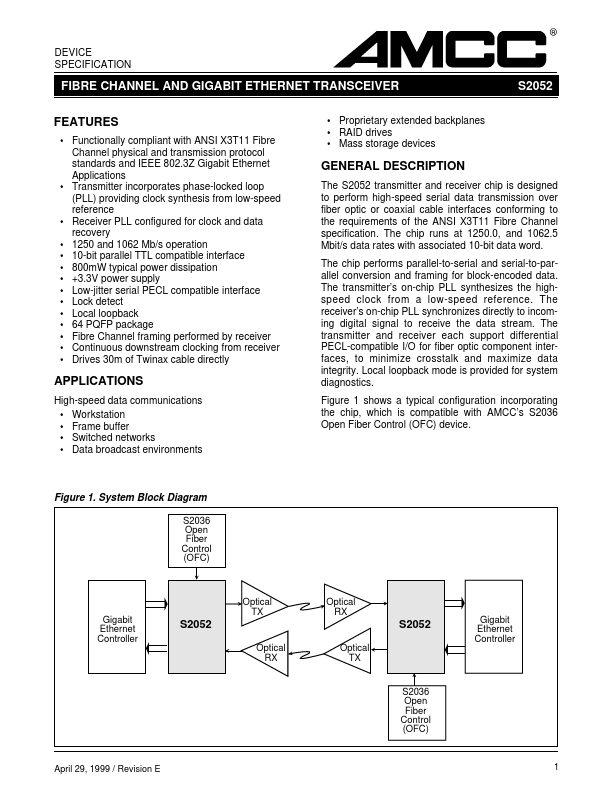

The S2052 transmitter and receiver chip is designed to perform high-speed serial data transmission over fiber optic or coaxial cable interfaces conforming to the requirements of the ANSI X3T11 Fibre Channel specification. The chip runs at 1250.0, and 1062.5 Mbit/s data rates with associated 10-bit data word.

Key Features

- Transmitter incorporates phase-locked loop (PLL) providing clock synthesis from low-speed reference

- Receiver PLL configured for clock and data recovery

- 1250 and 1062 Mb/s operation

- 10-bit parallel TTL compatible interface

- 800mW typical power dissipation

- +3.3V power supply

- Low-jitter serial PECL compatible interface

- Local loopback

- 64 PQFP package

- Fibre Channel framing performed by receiver