AN36

AN36 is CMOS Gate Array manufactured by AMI.

- Part of the AN31 comparator family.

- Part of the AN31 comparator family.

Core Logic

$1[

®

$0,+- PLFURQ &026

- DWH $UUD

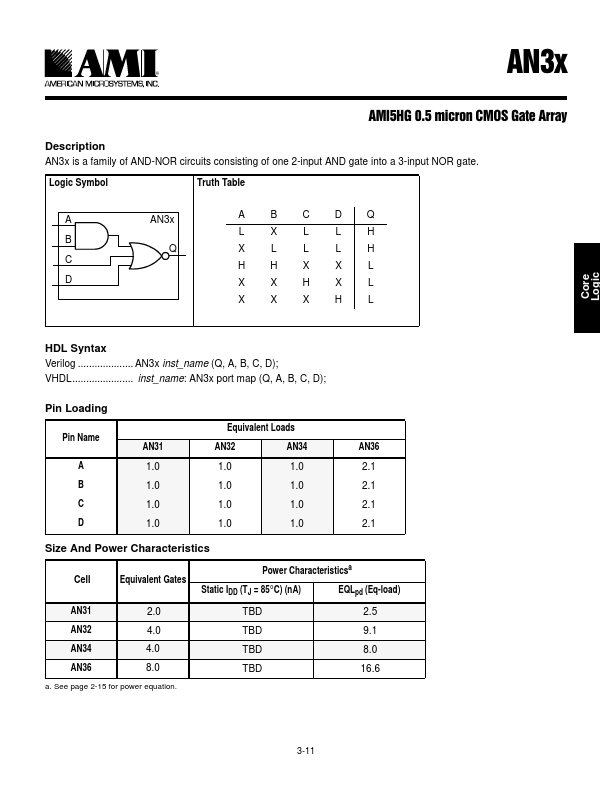

Description AN3x is a family of AND-NOR circuits consisting of one 2-input AND gate into a 3-input NOR gate.

Logic Symbol

Truth Table

AN3x

A B CDQ

LXL LH B

Q XLLLH

C HHXX L

D XXHXL

XXXHL

HDL Syntax Verilog .................... AN3x inst_name (Q, A, B, C, D); VHDL...................... inst_name: AN3x port map (Q, A, B, C, D);

Pin Loading

Pin Name

AN31 1.0 1.0 1.0 1.0

Equivalent Loads

AN32

AN34

1.0 1.0

1.0 1.0

1.0 1.0

1.0 1.0

AN36 2.1 2.1 2.1 2.1

Size And Power Characteristics

Power Characteristicsa

Cell Equivalent...