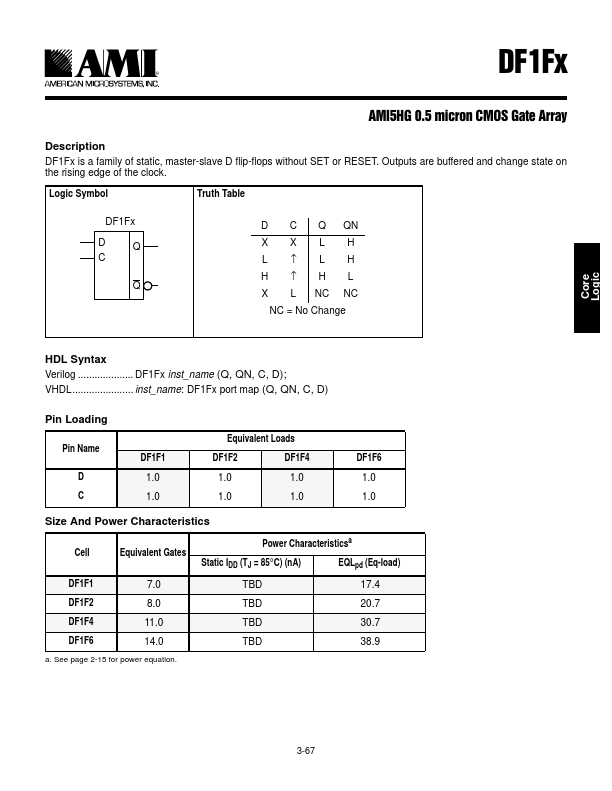

- Part: DF1F2

- Description: CMOS Gate Array

- Manufacturer: AMI

- Size: 36.88 KB

Datasheets by Manufacturer

| Part Number | Manufacturer | Description |

|---|---|---|

| DF15NC15 | Shindengen | Schottky Barrier Diode |

| DF110S | Thermtrol Corporation | DF SERIES 15 AMP THERMAL CUTOFFS |

| DF119S | Thermtrol Corporation | DF SERIES 15 AMP THERMAL CUTOFFS |

| DF128S | Thermtrol Corporation | DF SERIES 15 AMP THERMAL CUTOFFS |

| DF139S | Thermtrol Corporation | DF SERIES 15 AMP THERMAL CUTOFFS |

| DF141S | Thermtrol Corporation | DF SERIES 15 AMP THERMAL CUTOFFS |

| DF144S | Thermtrol Corporation | DF SERIES 15 AMP THERMAL CUTOFFS |

| DF152S | Thermtrol Corporation | DF SERIES 15 AMP THERMAL CUTOFFS |

| DF184S | Thermtrol Corporation | DF SERIES 15 AMP THERMAL CUTOFFS |

| DF192S | Thermtrol Corporation | DF SERIES 15 AMP THERMAL CUTOFFS |