FS6261-01

FS6261-01 is Motherboard Clock Generator manufactured by AMI.

Features

®

Description

Generates clocks required for Intel i820 based desktop and workstation systems, including: Four enabled 2.5V 133/100MHz CPU Front Side Bus (FSB) clocks Two 2.5V CPU/2 clocks for synchronous memory Seven enabled 3.3V PCI bus clocks and one free-running PCI clock Four enabled 3.3V 66MHz AGP clocks Three 2.5V 16.67MHz APIC bus clocks Two 3.3V 14.318MHz REF clocks One 3.3V 48MHz USB clock

The FS6261-01 is a CMOS clock generator IC designed for high-speed motherboard applications. Two different frequencies can be selected for the CPU clocks via two SEL pins. Glitch-free stop clock control of the CPU, AGP (66MHz) and PCI clocks is provided. A low current power-down mode is available for mobile applications. Separate clock buffers provide for a 2.5V voltage range on the CPU_0:3, CPU/2_0:1 and APIC_0:2 clocks.

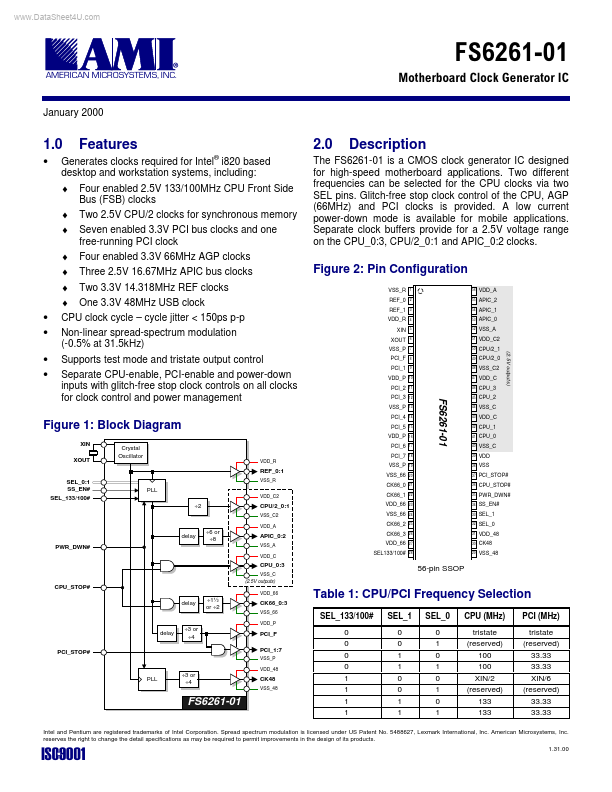

Figure 2: Pin Configuration

VSS_R REF_0 REF_1 VDD_R XIN XOUT VSS_P PCI_F PCI_1 VDD_P PCI_2 PCI_3 VSS_P PCI_4

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33 32 31 30 29

VDD_A APIC_2 APIC_1 APIC_0 VSS_A VDD_C2 CPU/2_1 CPU/2_0 VSS_C2 VDD_C CPU_3 CPU_2 VSS_C VDD_C CPU_1 CPU_0 VSS_C VDD VSS PCI_STOP# CPU_STOP# PWR_DWN# SS_EN# SEL_1 SEL_0 VDD_48 CK48 VSS_48

CPU clock cycle

- cycle jitter < 150ps p-p Non-linear spread-spectrum modulation (-0.5% at 31.5k Hz) Supports test mode and tristate output control Separate CPU-enable, PCI-enable and power-down inputs with glitch-free stop clock controls on all clocks for clock control and power management

(2.5V outputs)

Figure 1: Block Diagram

XIN XOUT Crystal Oscillator

VDD_R

PCI_5 VDD_P PCI_6 PCI_7 VSS_P VSS_66 CK66_0

VDD_C2

REF_0:1 SEL_0:1 SS_EN# SEL_133/100#

VSS_R

PLL ÷2 CPU/2_0:1

VSS_C2 VDD_A

CK66_1 VDD_66 VSS_66 CK66_2 CK66_3 VDD_66 SEL133/100# delay PWR_DWN#

÷6 or ÷8

APIC_0:2

VSS_A VDD_C

CPU_0:3

VSS_C (2.5V outputs)

56-pin SSOP

CPU_STOP#

VDD_66 delay

÷1½ or ÷2

Table 1:...