Datasheet Summary

LP62S4096E-I Series

512K X 8 BIT LOW VOLTAGE CMOS SRAM

Document Title 512K X 8 BIT LOW VOLTAGE CMOS SRAM Revision History

Rev. No.

History

Change VCCmax from 3.3V to 3.6V Add product family and 55ns specification

Issue Date

January 25, 2002

Remark

(January, 2002, Version 2.0)

AMIC Technology, Inc.

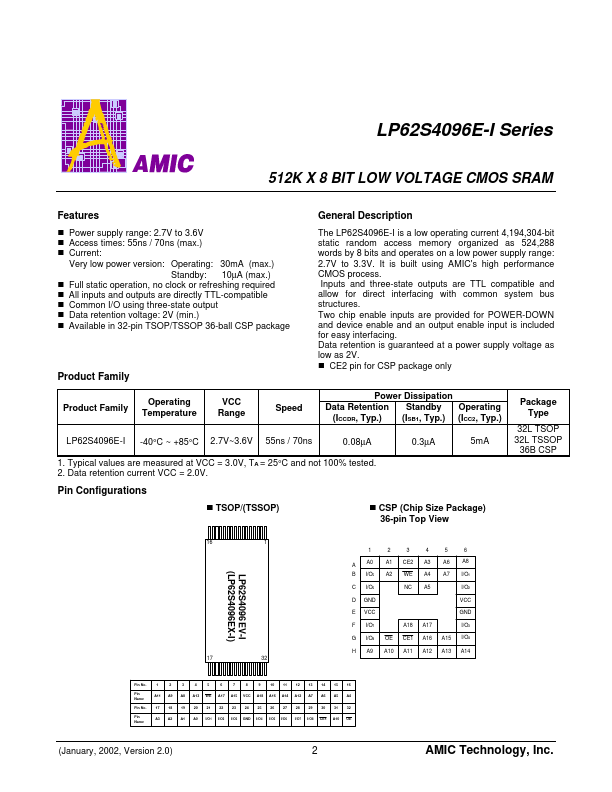

LP62S4096E-I Series

512K X 8 BIT LOW VOLTAGE CMOS SRAM

Features n Power supply range: 2.7V to 3.6V n Access times: 55ns / 70ns (max.) n Current: Very low power version: Operating: 30mA (max.) Standby: 10µA (max.) n Full static operation, no clock or refreshing required n All inputs and outputs are directly TTL-patible n mon I/O using three-state output n Data retention voltage:...