MT5C1008

MT5C1008 is 128K x 8 SRAM WITH DUAL CHIP ENABLE AVAILABLE AS MILITARY SPECIFICATIONS manufactured by ASI.

SRAM

Austin Semiconductor, Inc. 128K x 8 SRAM

WITH DUAL CHIP ENABLE

AVAILABLE AS MILITARY SPECIFICATIONS

- SMD 5962-89598

- MIL-STD-883

NC A16 A14 A12 A7 A6 A5 A4 A3 A2 A1 A0 DQ1 DQ2 DQ3 VSS 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

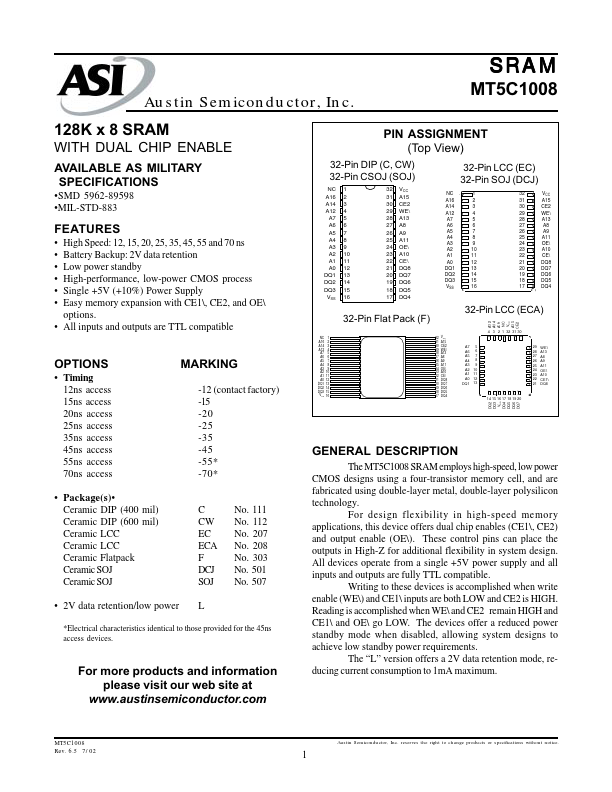

PIN ASSIGNMENT (Top View)

32-Pin DIP (C, CW) 32-Pin CSOJ (SOJ)

32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 VCC A15 CE2 WE A13 A8 A9 A11 OE A10 CE DQ8 DQ7 DQ6 DQ5 DQ4

NC A16 A14 A12 A7 A6 A5 A4 A3 A2 A1 A0 DQ1 DQ2 DQ3 VSS

32-Pin LCC (EC) 32-Pin SOJ (DCJ)

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 VCC A15 CE2 WE A13 A8 A9 A11 OE A10 CE DQ8 DQ7 DQ6 DQ5 DQ4

Features

- -

- -

- - High Speed: 12, 15, 20, 25, 35, 45, 55 and 70 ns Battery Backup: 2V data retention Low power standby High-performance, low-power CMOS process Single +5V (+10%) Power Supply Easy memory expansion with CE1, CE2, and OE options.

- All inputs and outputs are TTL patible

32-Pin LCC (ECA)

4 3 2 1 32 31 30

NC A16 A14 A12 A7 A6 A5 A4 A3 A2 A1 A0 DQ1 DQ2 DQ3 VSS 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 32 31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 VCC A15 CE2 WE A13 A8 A9 A11 OE A10 CE DQ8 DQ7 DQ6 DQ5 DQ4

OPTIONS

- Timing 12ns access 15ns access 20ns access 25ns access 35ns access 45ns access 55ns access 70ns access

- Package(s)- Ceramic DIP (400 mil) Ceramic DIP (600 mil) Ceramic LCC Ceramic LCC Ceramic Flatpack Ceramic SOJ Ceramic SOJ

- 2V data retention/low power

MARKING

-12 (contact factory) -15 -20 -25 -35 -45 -55- -70-

A7 A6 A5 A4 A3 A2 A1 A0 DQ1

5 6 7 8 9 10 11 12 13

A12 A14 A10 6 NC VCC A15...