Datasheet Summary

Features

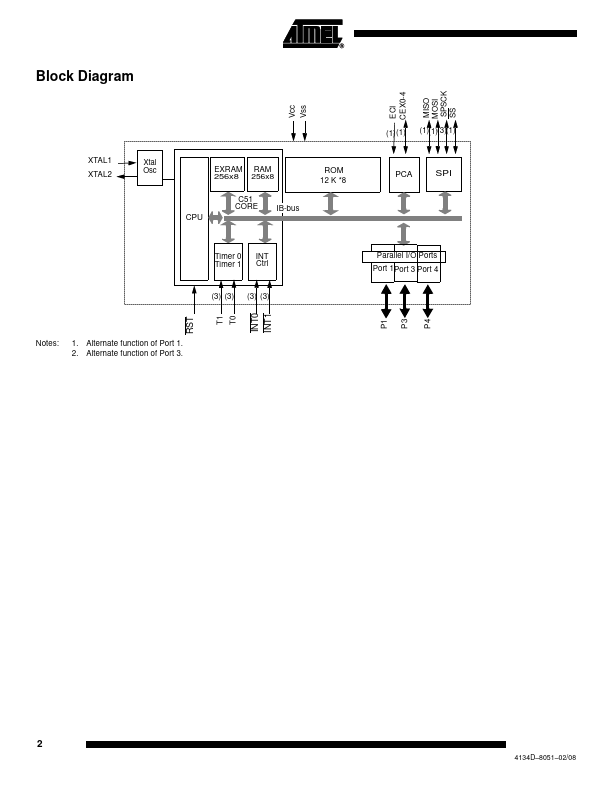

- 80C51 patible CPU Core High-speed Architecture

- X2 Speed Improvement Capability (6 Clocks/Machine Cycle)

- 16 MHz in Standard or X2 mode

- 256 Bytes RAM

- 256 Bytes XRAM

- 12K Bytes ROM/OTP Program Memory

- Two 16-bit Timer/Counters T0, T1

- 5 Channels Programmable Counter Array with High-speed Output, pare/Capture,

Pulse Width Modulation and Watchdog Timer Capabilities

- SPI Interface (Master and Slave mode)

- Interrupt Structure with:

- 6 Interrupt Sources

- 4 Interrupt Priority Levels

- Power Supply: 3

- 5.5V

- Temperature Range: Industrial (-40oC to 85oC), Automotive (-40oC to 125oC)

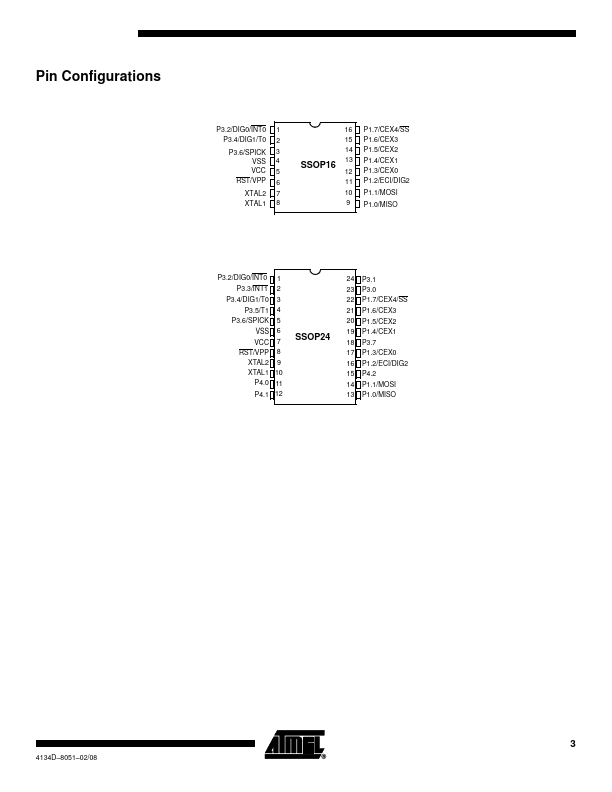

- Package: SSOP16, SSOP24

Description

The AT8xC5103 is a high-performance ROM/OTP...