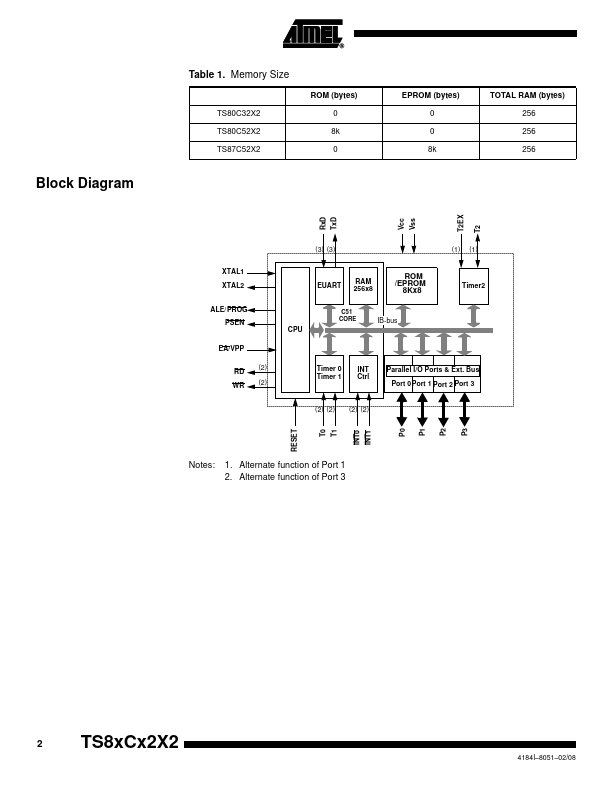

Datasheet Summary

Features

- 80C52 patible

- 8051 Pin and Instruction patible

- Four 8-bit I/O Ports

- Three 16-bit Timer/Counters

- 256 Bytes Scratchpad RAM

- High-speed Architecture

- 40 MHz at 5V, 30 MHz at 3V

- X2 Speed Improvement Capability (6 Clocks/Machine Cycle)

- 30 MHz at 5V, 20 MHz at 3V (Equivalent to 60 MHz at 5V, 40 MHz at 3V)

- Dual Data Pointer

- On-chip ROM/EPROM (8Kbytes)

- Programmable Clock Out and Up/Down Timer/Counter 2

- Asynchronous Port Reset

- Interrupt Structure with

- 6 Interrupt Sources

- 4 Level Priority Interrupt System

- Full Duplex Enhanced UART

- Framing Error Detection

- Automatic Address Recognition

- Low EMI (Inhibit ALE)

- Power Control Modes

- Idle Mode

-...