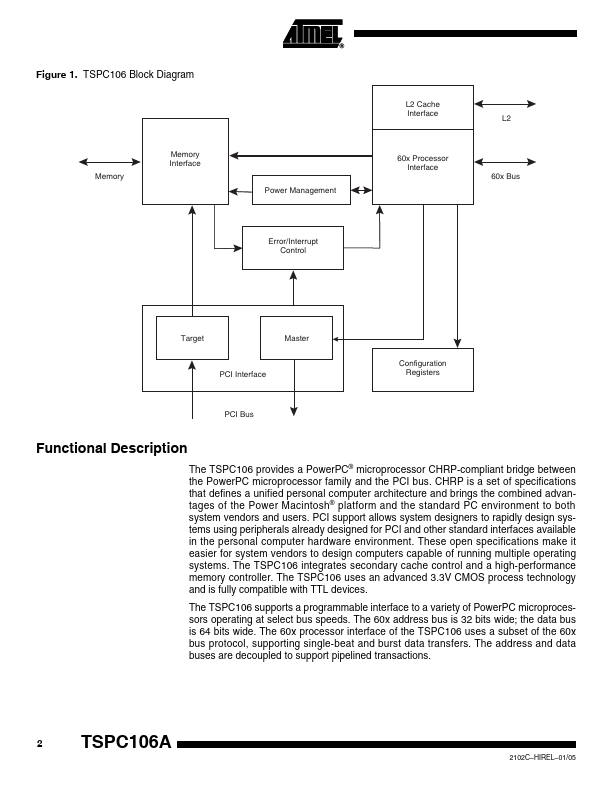

TSPC106 Description

The TSPC106 provides an integrated, high-bandwidth, high-performance, TTL-pa.

TSPC106 Key Features

- Processor Bus Frequency Up to 66 MHz and 83.3 MHz

- 64-bit Data Bus and 32-bit Address Bus

- L2 Cache Control for 256-Kbyte, 512-Kbyte, 1-Mbyte Sizes

- Provides Support for Either Asynchronous SRAM, Burst SRAM

- pliant with PCI Specification, Revision 2.1

- PCI Interface Operates at 20 to 33 MHz, 3.3V/5.0V-patible

- IEEE 1149.1-pliant, JTAG Boundary-scan Interface

- PD Max = 1.7 Watts (66 MHz), Full Operating Conditions

- Nap, Doze and Sleep Modes Reduce Power Consumption

- Fully pliant with MIL-STD-883 Class Q or According to Atmel Standards