A1010B Overview

Key Specifications

Package: PLCC

Mount Type: Surface Mount

Pins: 44

Operating Voltage: 5 V

Description

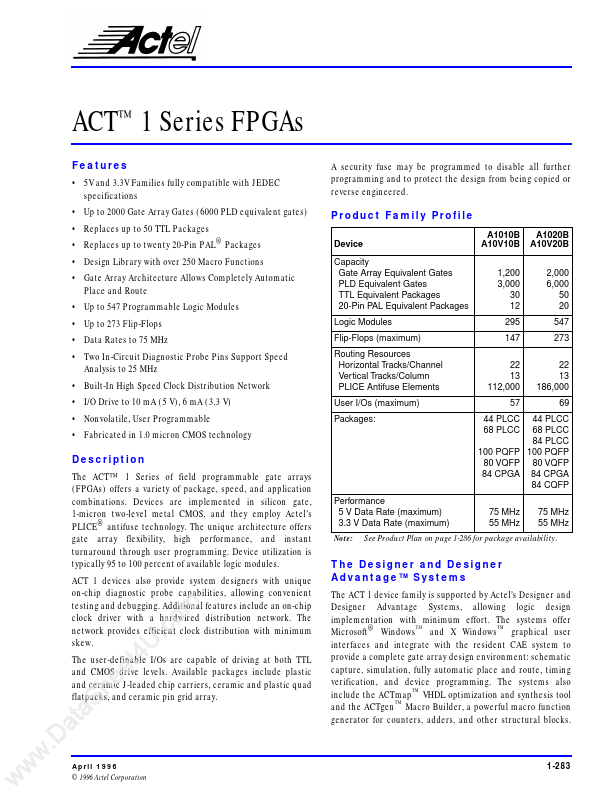

A security fuse may be programmed to disable all further programming and to protect the design from being copied or reverse engineered. Product Family Profile Device Capacity Gate Array Equivalent Gates PLD Equivalent Gates TTL Equivalent Packages 20-Pin PAL Equivalent Packages Logic Modules Flip-Flops (maximum) Routing Resources Horizontal Tracks/Channel Vertical Tracks/Column PLICE Antifuse Elements User I/Os (maximum) Packages: A1010B A10V10B 1,200 3,000 30 12 295 147 22 13 112,000 57 44 PLCC 68 PLCC A1020B A10V20B 2,000 6,000 50 20 547 273 22 13 186,000 69 The ACT™ 1 Series of field programmable gate arrays (FPGAs) offers a variety of package, speed, and application combinations.

Key Features

- 5V and 3.3V Families fully compatible with JEDEC specifications

- Up to 2000 Gate Array Gates (6000 PLD equivalent gates)

- Replaces up to 50 TTL Packages

- Replaces up to twenty 20-Pin PAL® Packages

- Design Library with over 250 Macro Functions

- Gate Array Architecture Allows Completely Automatic Place and Route

- Up to 547 Programmable Logic Modules

- Up to 273 Flip-Flops

- Data Rates to 75 MHz

- Two In-Circuit Diagnostic Probe Pins Support Speed Analysis to 25 MHz