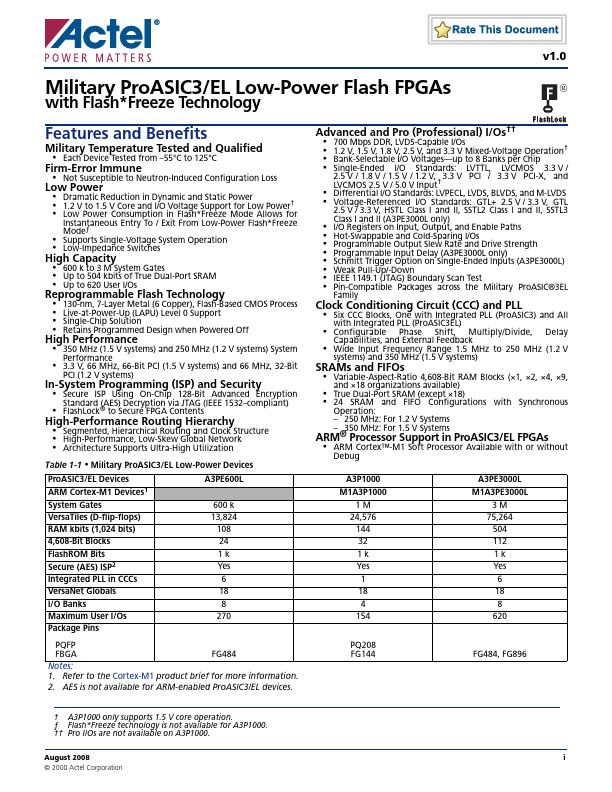

A3PE3000L

Overview

- Each Device Tested from -55°C to 125°C ® Advanced and Pro (Professional) I/Os†† * * * * * * * * * * * * *

- 700 Mbps DDR, LVDS-Capable I/Os 1.2 V, 1.5 V, 1.8 V, 2.5 V, and 3.3 V Mixed-Voltage Operation† Bank-Selectable I/O Voltages-up to 8 Banks per Chip Single-Ended I/O Standards: LVTTL, LVCMOS 3.3 V / 2.5 V / 1.8 V / 1.5 V / 1.2 V, 3.3 V PCI / 3.3 V PCI-X, and LVCMOS 2.5 V / 5.0 V Input† Differential I/O Standards: LVPECL, LVDS, BLVDS, and M-LVDS Voltage-Referenced I/O Standards: GTL+ 2.5 V / 3.3 V, GTL 2.5 V / 3.3 V, HSTL Class I and II, SSTL2 Class I and II, SSTL3 Class I and II (A3PE3000L only) I/O Registers on Input, Output, and Enable Paths Hot-Swappable and Cold-Sparing I/Os Programmable Output Slew Rate and Drive Strength Programmable Input Delay (A3PE3000L only) Schmitt Trigger Option on Single-Ended Inputs (A3PE3000L) Weak Pull-Up/-Down IEEE 1149.1 (JTAG) Boundary Scan Test Pin-Compatible Packages across the Military ProASIC®3EL Family Firm-Error Immune

- Not Susceptible to Neutron-Induced Configuration Loss Low Power

- Dramatic Reduction in Dynamic and Static Power

- 1.2 V to 1.5 V Core and I/O Voltage Support for Low Power†

- Low Power Consumption in Flash*Freeze Mode Allows for Instantaneous Entry To / Exit From Low-Power Flash*Freeze Modeƒ

- Supports Single-Voltage System Operation

- Low-Impedance Switches High Capacity

- 600 k to 3 M System Gates

- Up to 504 kbits of True Dual-Port SRAM