| Part | AX250 |

|---|---|

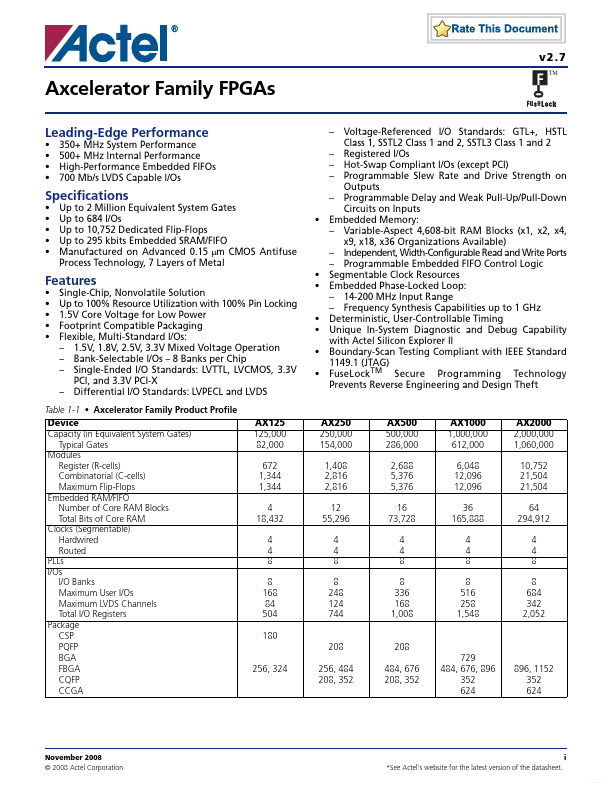

| Description | Axcelerator Family FPGAs |

| Manufacturer | Actel |

| Size | 2.40 MB |

Pricing from 335.53044 USD, available from DigiKey and Newark.

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| DigiKey | 0 | 90+ : 335.53044 USD | View Offer |

| Newark | 0 | 90+ : 335.53 USD 100+ : 330.87 USD 250+ : 317.63 USD 500+ : 301.55 USD |

View Offer |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| AX2535 | AXElite | High Precision CC/CV Primary-Side PWM Power Switch |

| AX2530 | AXElite | High Precision CC/CV Primary-Side PWM Power Switch |