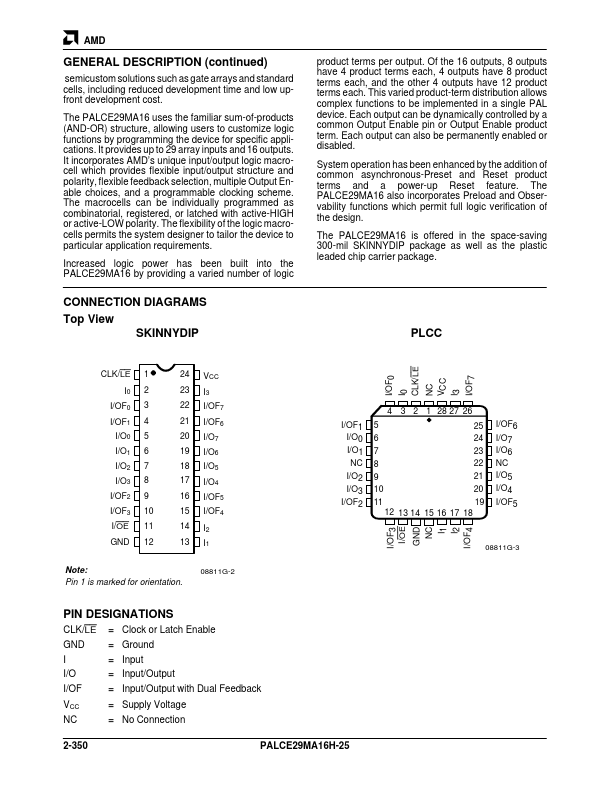

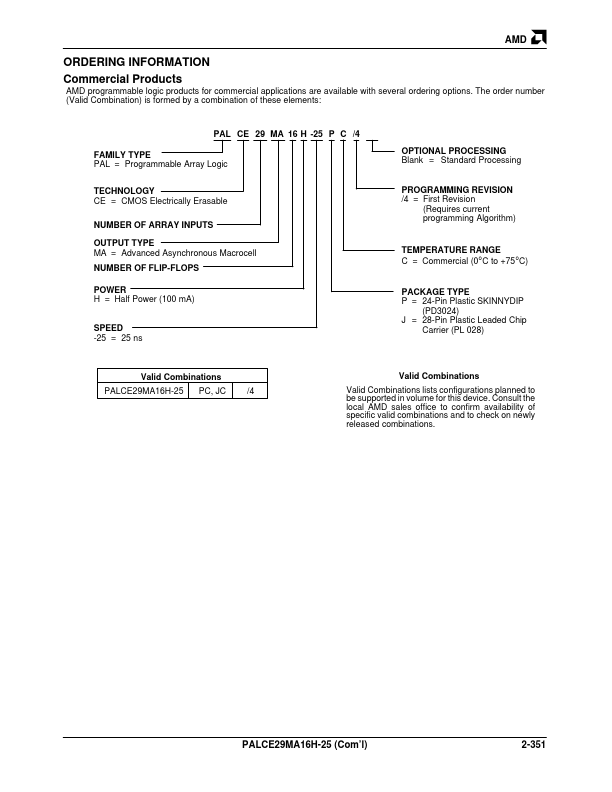

Datasheet Summary

FINAL

’L: H-25

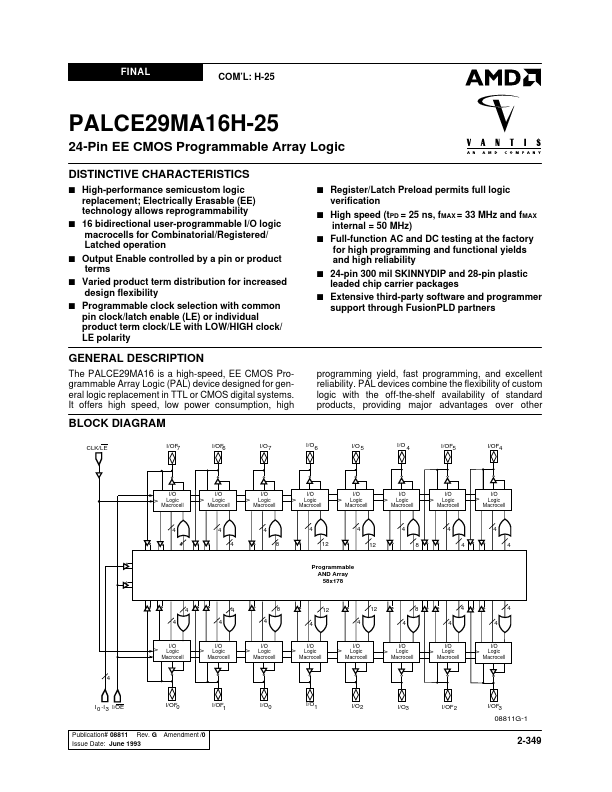

24-Pin EE CMOS Programmable Array Logic

DISTINCTIVE CHARACTERISTICS s High-performance semicustom logic s Register/Latch Preload permits full logic s s s s replacement; Electrically Erasable (EE) technology allows reprogrammability 16 bidirectional user-programmable I/O logic macrocells for binatorial/Registered/ Latched operation Output Enable controlled by a pin or product terms Varied product term distribution for increased design flexibility Programmable clock selection with mon pin clock/latch enable (LE) or individual product term clock/LE with LOW/HIGH clock/ LE polarity verification s High speed (tPD = 25 ns, fMAX = 33 MHz and fMAX...