UT54ACS109E

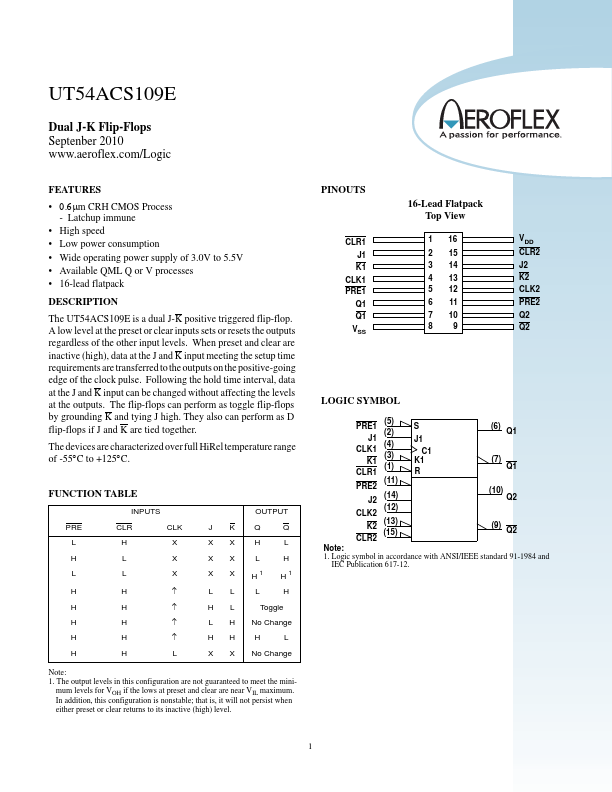

UT54ACS109E is Dual J-K Flip-Flops manufactured by Aeroflex Circuit Technology.

FEATURES

- 0.6μm CRH CMOS Process

- Latchup immune

- High speed

- Low power consumption

- Wide operating power supply of 3.0V to 5.5V

- Available QML Q or V processes

- 16-lead flatpack

DESCRIPTION

The UT54ACS109E is a dual J-K positive triggered flip-flop. A low level at the preset or clear inputs sets or resets the outputs regardless of the other input levels. When preset and clear are inactive (high), data at the J and K input meeting the setup time requirements are transferred to the outputs on the positive-going edge of the clock pulse. Following the hold time interval, data at the J and K input can be changed without affecting the levels at the outputs. The flip-flops can perform as toggle flip-flops by grounding K and tying J high. They also can perform as D flip-flops if J and K are tied together.

The devices are characterized over full Hi Rel temperature range of -55°C to +125°C.

FUNCTION TABLE

PRE L H L

H H H H H

INPUTS

H↑ H↑ H↑ H↑ HL

OUTPUT

JK Q

XX H

XX L

X X H1 H1

Toggle

L H No Change

HH H

X X No Change

Note: 1. The output levels in this configuration are not guaranteed to meet the mini- mum levels for VOH if the lows at preset and clear are near VIL maximum. In addition, this configuration is nonstable; that is, it will not persist when either preset or clear returns to its inactive (high)...