OR3TP12

Overview

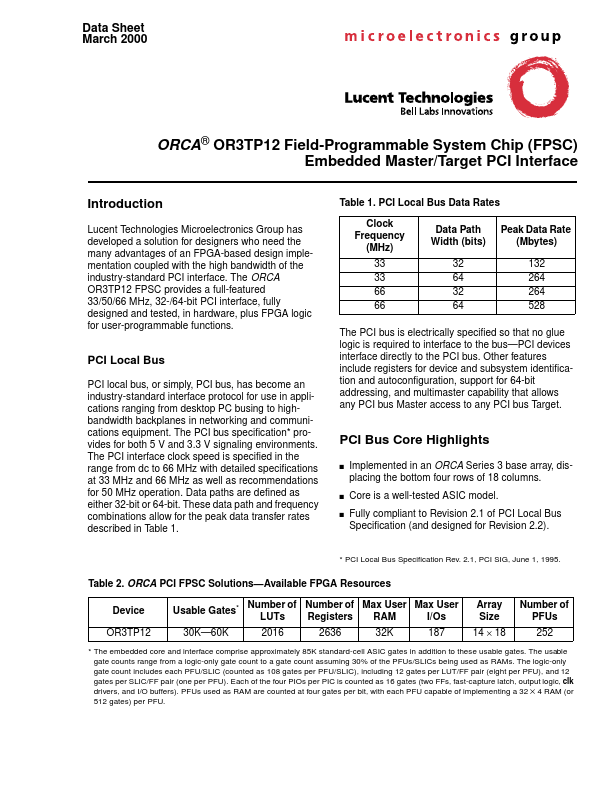

Lucent Technologies Microelectronics Group has developed a solution for designers who need the many advantages of an FPGA-based design implementation coupled with the high bandwidth of the industry-standard PCI interface. The ORCA OR3TP12 FPSC provides a full-featured 33/50/66 MHz, 32-/64-bit PCI interface, fully designed and tested, in hardware, plus FPGA logic for user-programmable functions.

- PCI Local Bus Specification Rev. 2.1, PCI SIG, June 1,