OR4E2

Key Features

- ZBT is a trademark of Integrated Device Technologies Inc. † RapidIO is a trademark of Motorola, Inc. Table

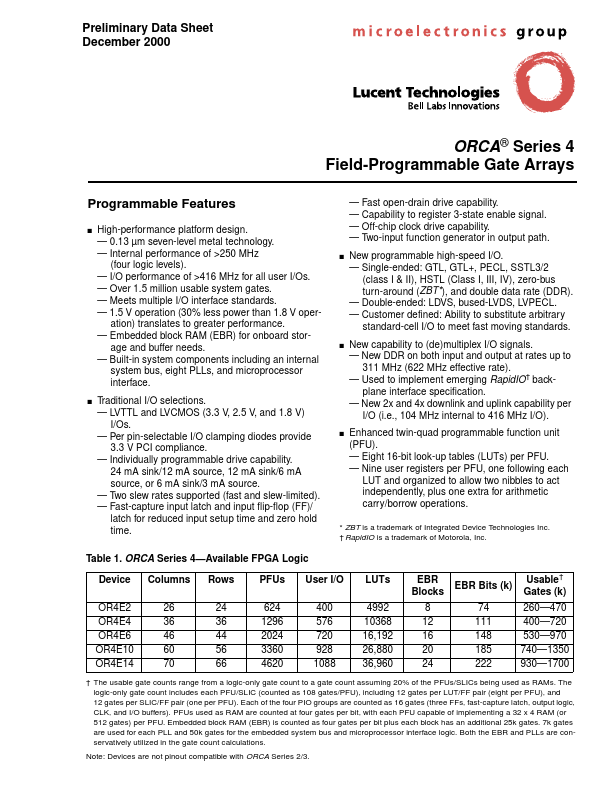

- ORCA Series 4-Available FPGA Logic Device OR4E2 OR4E4 OR4E6 OR4E10 OR4E14 Columns 26 36 46 60 70 Rows 24 36 44 56 66 PFUs 624 1296 2024 3360 4620 User I/O 400 576 720 928 1088 LUTs 4992 10368 16,192 26,880 36,960 EBR Blocks 8 12 16 20 24 EBR Bits (k) 74 111 148 185 222 Usable† Gates (k) 260-470 400-720 530-970 740-1350 930-1700 † The usable gate counts range from a logic-only gate count to a gate count assuming 20% of the PFUs/SLICs being used as RAMs. The logic-only gate count includes each PFU/SLIC (counted as 108 gates/PFU), including 12 gates per LUT/FF pair (eight per PFU), and 12 gates per SLIC/FF pair (one per PFU). Each of the four PIO groups are counted as 16 gates (three FFs, fast-capture latch, output logic, CLK, and I/O buffers). PFUs used as RAM are counted at four gates per bit, with each PFU capable of implementing a 32 x 4 RAM (or 512 gates) per PFU. Embedded block RAM (EBR) is counted as four gates per bit plus each block has an additional 25k gates. 7k gates are used for each PLL and 50k gates for the embedded system bus and microprocessor interface logic. Both the EBR and PLLs are conservatively utilized in the gate count calculations. Note: Devices are not pinout compatible with ORCA Series 2/3. ORCA Series 4 FPGAs Preliminary Data Sheet December 2000 Table of Contents Contents Page Contents Page Figure Page