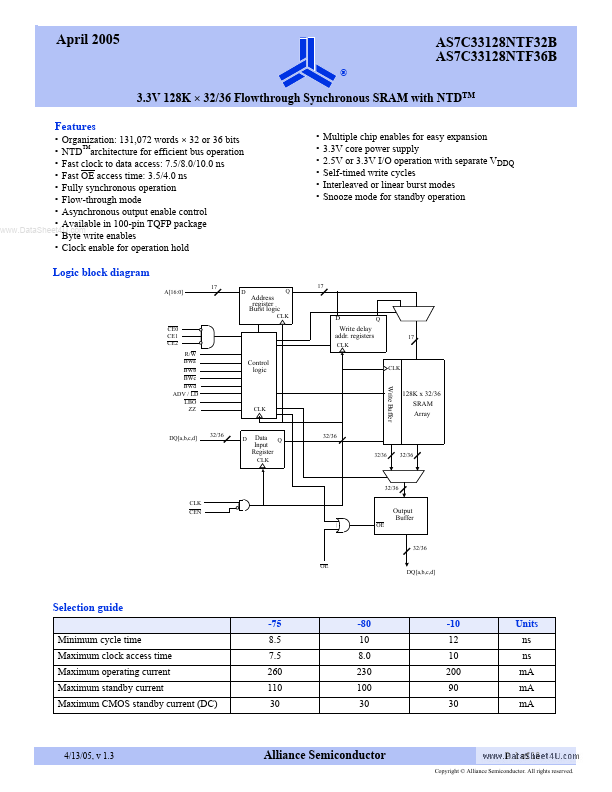

AS7C33128NTF32B Overview

Key Features

- Organization: 131,072 words × 32 or 36 bits

- NTD™architecture for efficient bus operation

- Fast clock to data access: 7.5/8.0/10.0 ns

- Fast OE access time: 3.5/4.0 ns

- Fully synchronous operation

- Flow-through mode

- Asynchronous output enable control

- Available in 100-pin TQFP package

- Clock enable for operation hold