AS7C33512NTD18A

AS7C33512NTD18A is 3.3V 512K x 18 Pipelined burst Synchronous SRAM manufactured by Alliance Semiconductor Corporation.

November 2004

®

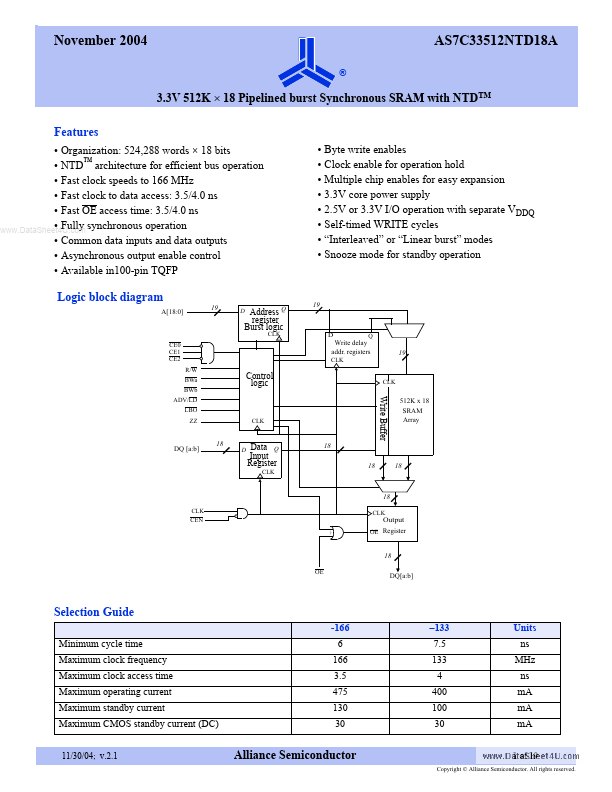

3.3V 512K × 18 Pipelined burst Synchronous SRAM with NTDTM Features

- Organization: 524,288 words × 18 bits

- NTD™ architecture for efficient bus operation

- Fast clock speeds to 166 MHz

- Fast clock to data access: 3.5/4.0 ns

- Fast OE access time: 3.5/4.0 ns

- Fully synchronous operation ..

- mon data inputs and data outputs

- Asynchronous output enable control

- Available in100-pin TQFP

- Byte write enables

- Clock enable for operation hold

- Multiple chip enables for easy expansion

- 3.3V core power supply

- 2.5V or 3.3V I/O operation with separate VDDQ

- Self-timed WRITE cycles

- “Interleaved” or “Linear burst” modes

- Snooze mode...