ASM5P2304A

ASM5P2304A is 3.3V Zero Delay Buffer manufactured by Alliance Semiconductor Corporation.

Features

Zero input

- output propagation delay, adjustable by capacitive load on FBK input. Multiple configurations

- Refer “ASM5P2304A Configurations Table”. Input frequency range: 15MHz to 133MHz Multiple low-skew outputs. Output-output skew less than 200p S. Device-device skew less than 500p S. Two banks of four outputs. Less than 200p S Cycle-to-Cycle jitter (-1, -1H, -2, -2H). Available in space saving, 8 pin 150-mil SOIC packages. 3.3V operation. Advanced 0.35< CMOS technology. Industrial temperature available. the REF pin. The PLL feedback is required to be driven to FBK pin, and can be obtained from one of the outputs. The input-to-output propagation delay is guaranteed to be less than 250p S, and the output-to-output skew is guaranteed to be less than 200p S. The ASM5P2304A has two banks of two outputs each. Multiple ASM5P2304A devices can accept the same input clock and distribute it. In this case the skew between the outputs of the two devices is guaranteed to be less than 500p S. The ASM5P2304A is available in two different configurations (Refer “ASM5P2304A Configurations Table). The ASM5P2304A-1 is the base part, where the output frequencies equal the reference if there is no counter in the feedback path. The ASM5P2304A-1H is the high-drive version of the -1 and the rise and fall times on this device are much faster. The ASM5P2304A-2 allows the user to obtain REF and 1/2X or 2X frequencies on each output bank. The exact configuration and output frequencies depend on which output drives the feedback pin.

Functional Description

ASM5P2304A is a versatile, 3.3V zero-delay buffer designed to distribute high-speed clocks in PC, workstation, data, tele and other high-performance applications. It is available in 8 pin package. The part has an on-chip PLL which locks to an input clock presented on

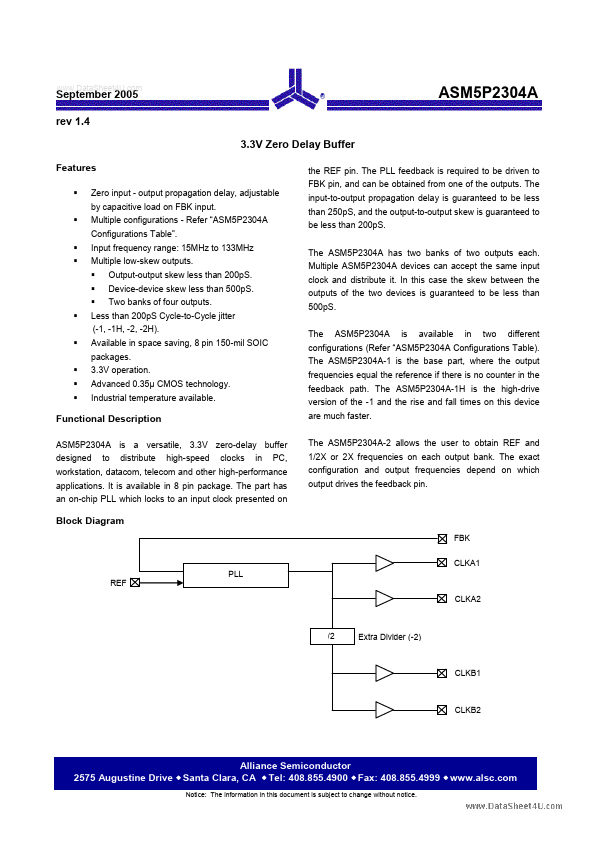

Block Diagram

FBK CLKA1 REF PLL CLKA2

/2

Extra Divider (-2)

CLKB1

CLKB2

Alliance Semiconductor 2575 Augustine Drive

- Santa Clara, CA

- Tel: 408.855.4900

- Fax:...