ASM5P2304A

Overview

- Zero Input-Output Propagation Delay, Adjustable by Capacitive Load on FBK Input

- Multiple Configurations - Refer to ASM5P2304A Configurations Table

- Input Frequency Range: 10 MHz to 133 MHz - Multiple Low-skew Outputs - Output-Output Skew less than 200 pS - Device-Device Skew less than 500 pS - Two Banks of Two Outputs Each

- Less than 200 pS Cycle-to-Cycle Jitter (-1, -1H, -2, -2H)

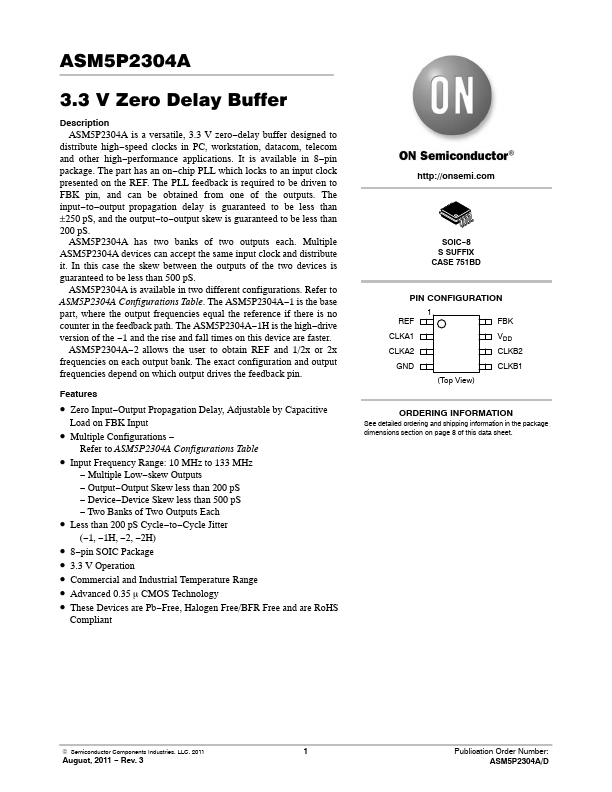

- 8-pin SOIC Package

- 3.3 V Operation

- Commercial and Industrial Temperature Range

- Advanced 0.35 m CMOS Technology

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant htt