ASM5P2305A

ASM5P2305A is 3.3V Zero Delay Buffer manufactured by Alliance Semiconductor Corporation.

Features

- -

- 15MHz to 133MHz operating range, patible with CPU and PCI bus frequencies. Zero input

- output propagation delay. Multiple low-skew outputs.

- -

- -

- -

- Output-output skew less than 250p S. Device-device skew less than 700p S. One input drives 9 outputs, grouped as 4 + 4 + 1(ASM5P2309A). One input drives 5 outputs (ASM5P2305A). Less than 200 p S cycle-to-cycle jitter is patible with Pentium® based systems. Test Mode to bypass PLL (ASM5P2309A only, Refer Select Input Decoding Table). Available in 16pin 150-mil SOIC, 4.4 mm TSSOP (ASM5P2309A), and in 8pin 150-mil SOIC package (ASM5P2305A).

- 3.3V operation, advanced 0.35µ CMOS technology.

133MHz frequencies, and has higher drive than the -1 devices. All parts have on-chip PLLs that lock to an input clock on the REF pin. The PLL feedback is on-chip and is obtained from the CLKOUT pad. The ASM5P2309A has two banks of four outputs each, which can be controlled by the Select inputs as shown in the Select Input Decoding Table. The select input also allows the input clock to be directly applied to the outputs for chip and system testing purposes. Multiple ASM5P2309A and ASM5P2305A devices can accept the same input clock and distribute it. In this case the skew between the outputs of the two devices is guaranteed to be less than 700p S. All outputs have less than 200p S of cycle-to-cycle jitter. The input and output propagation delay is guaranteed to be less than 350p S, and the output to output skew is guaranteed to be less than 250p S. The ASM5P2309A and the ASM5P2305A are available in two different configurations, as shown in the ordering information table. The ASM5P2305A-1/ ASM5P2309A-1 is the base part. The ASM5P2305A-1H/ ASM5P2309A-1H is the high drive version of the -1 and its rise and fall times are much faster than -1 part.

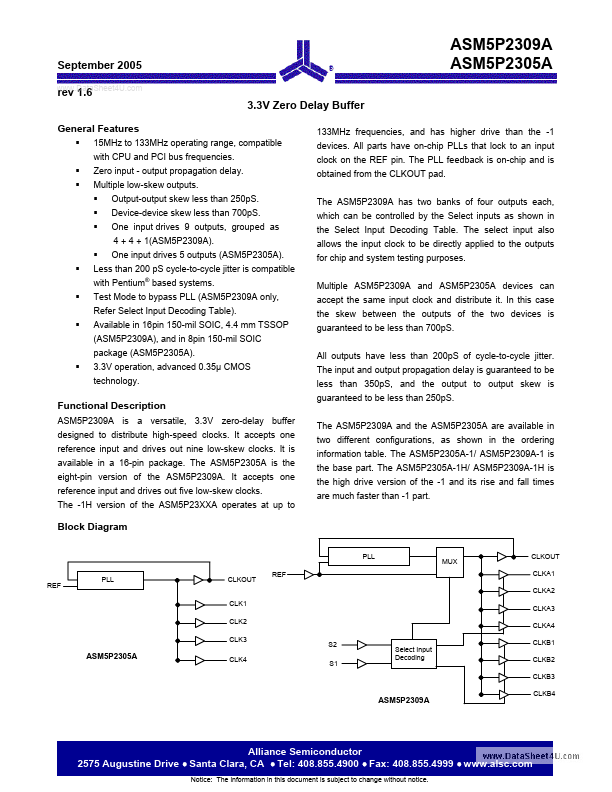

Functional Description

ASM5P2309A is a versatile, 3.3V zero-delay buffer designed to distribute high-speed clocks. It accepts one reference input and drives out nine low-skew clocks....