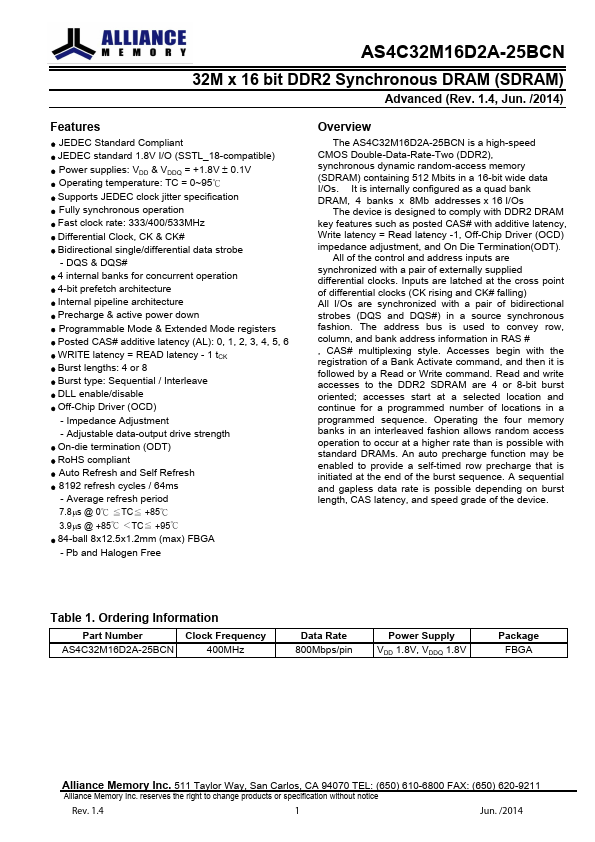

Datasheet Summary

32M x 16 bit DDR2 Synchronous DRAM (SDRAM)

Advanced (Rev. 1.4, Jun. /2014)

Features

- JEDEC Standard pliant

- JEDEC standard 1.8V I/O (SSTL_18-patible)

- Power supplies: VDD & VDDQ = +1.8V ± 0.1V

- Operating temperature: TC = 0~95℃

- Supports JEDEC clock jitter specification

- Fully synchronous operation

- Fast clock rate: 333/400/533MHz

- Differential Clock, CK & CK#

- Bidirectional single/differential data strobe

- DQS & DQS#

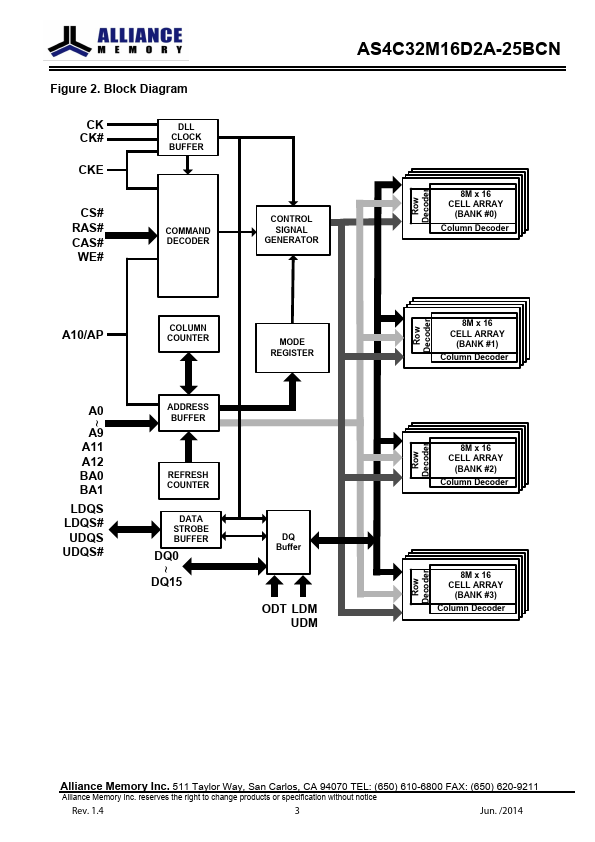

- 4 internal banks for concurrent operation

- 4-bit prefetch architecture

- Internal pipeline architecture

- Precharge & active power down

- Programmable Mode & Extended Mode registers

- Posted CAS# additive latency (AL): 0, 1, 2, 3, 4, 5,...