Datasheet Summary

AS4C32M16D2C-25BCN AS4C32M16D2C-25BIN

Revision History 512M DDR2 AS4C32M16D2C

Revision Details Rev 1.0 Initial release

84ball FBGA PACKAGE

Date June. 2022

Confidential

-163-

Rev.1.0 June 2022

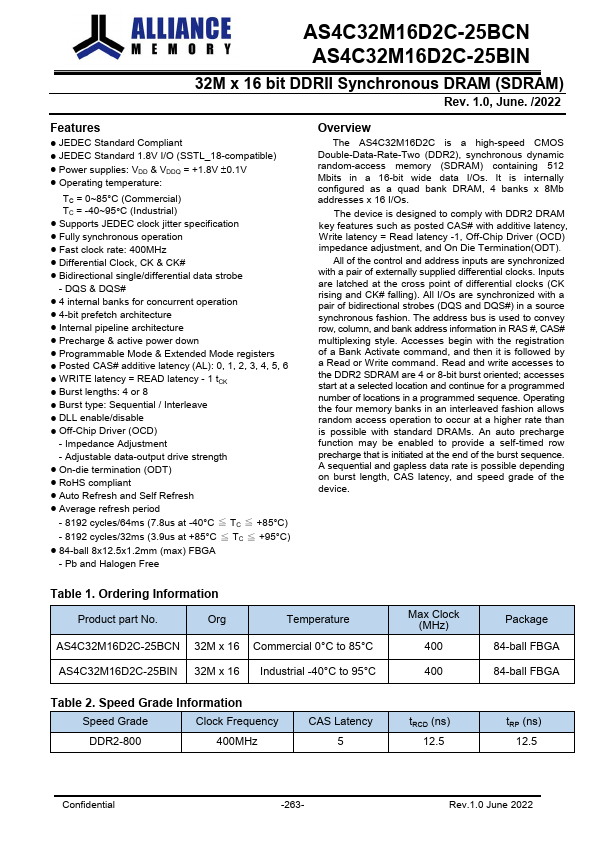

AS4C32M16D2C-25BCN AS4C32M16D2C-25BIN

32M x 16 bit DDRII Synchronous DRAM (SDRAM)

Rev. 1.0, June. /2022

Features

- JEDEC Standard pliant

- JEDEC Standard 1.8V I/O (SSTL_18-patible)

- Power supplies: VDD & VDDQ = +1.8V 0.1V

- Operating temperature:

TC = 0~85°C (mercial) TC = -40~95°C (Industrial)

- Supports JEDEC clock jitter specification

- Fully synchronous operation

- Fast clock rate: 400MHz

- Differential Clock, CK & CK#

- Bidirectional single/differential data strobe

- DQS & DQS#

-...