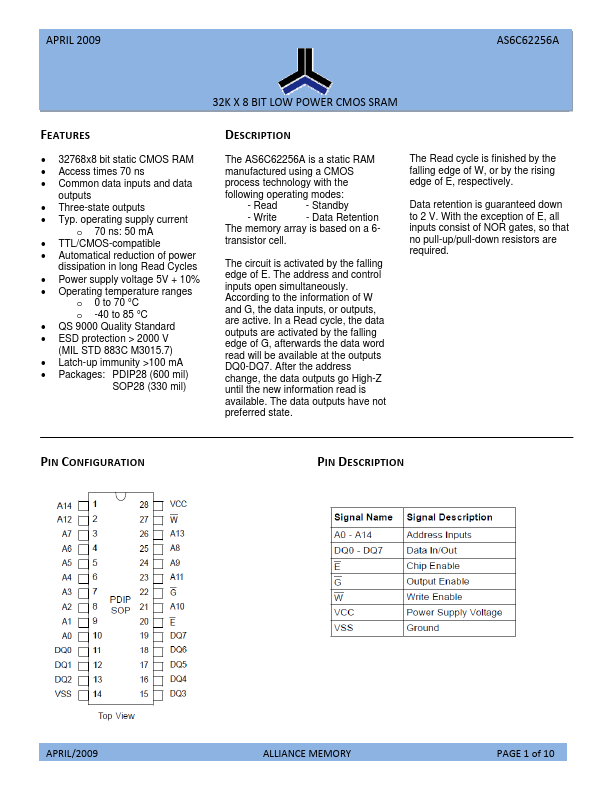

AS6C62256A Key Features

- 32768x8 bit static CMOS RAM

- Access times 70 ns

- mon data inputs and data

- Three-state outputs

- Typ. operating supply current

- TTL/CMOS-patible

- Automatical reduction of power

- Power supply voltage 5V + 10%

- Operating temperature ranges

- QS 9000 Quality Standard