EPM7256B Overview

Key Specifications

Package: PQFP

Mount Type: Surface Mount

Pins: 208

Operating Voltage: 2.5 V

Key Features

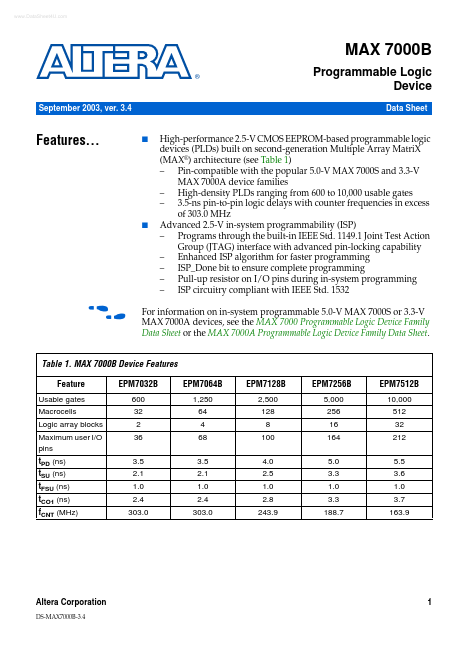

- High-performance 2.5-V CMOS EEPROM-based programmable logic devices (PLDs) built on second-generation Multiple Array MatriX (MAX®) architecture (see Table 1)

- Pin-compatible with the popular 5.0-V MAX 7000S and 3.3-V MAX 7000A device families