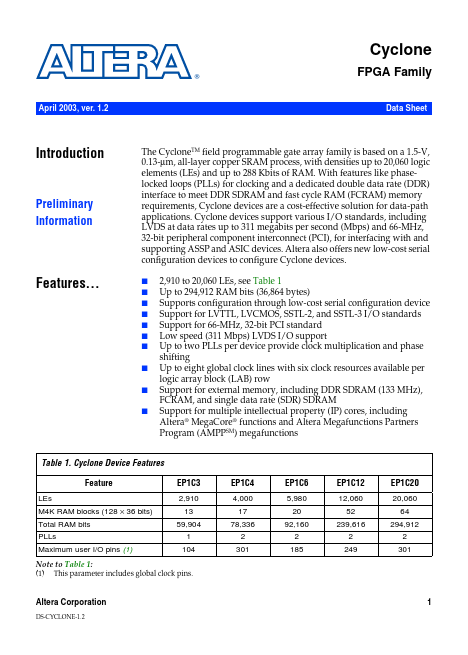

| Part | EP1C12 |

|---|---|

| Description | FPGA |

| Manufacturer | Altera |

| Size | 1.08 MB |

Pricing from 109.498 USD, available from CoreStaff and Verical.Powered by Octopart

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| CoreStaff | 91 | 1+ : 109.498 USD 2+ : 106.141 USD 3+ : 105.022 USD 4+ : 104.462 USD |

View Offer |

| CoreStaff | 29 | 1+ : 57.794 USD 2+ : 54.471 USD 3+ : 53.363 USD 4+ : 52.809 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| HFDOM44P-xxxSx | Hanbit Electronics | 44Pin Flash Disk Module |

| HFDOM40B-xxxSx | Hanbit Electronics | 40Pin Flash Disk Module |

| CP2105 | Silicon Labs | SINGLE-CHIP USB TO DUAL UART BRIDGE |