AD5684R Overview

Key Specifications

Package: TSSOP

Pins: 16

Max Voltage (typical range): 5.5 V

Min Voltage (typical range): 2.7 V

Description

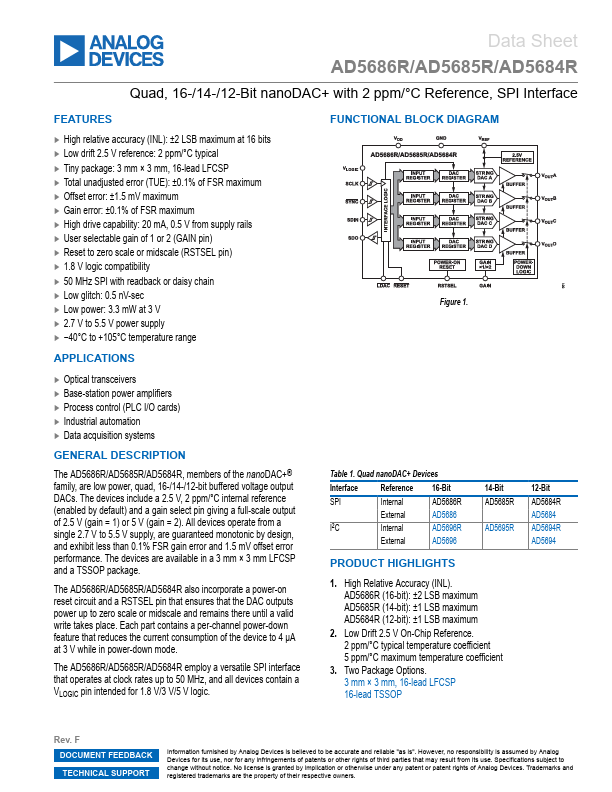

The AD5686R/AD5685R/AD5684R, members of the nanoDAC+® family, are low power, quad, 16-/14-/12-bit buffered voltage output DACs. The devices include a 2.5 V, 2 ppm/°C internal reference (enabled by default) and a gain select pin giving a full-scale output of 2.5 V (gain = 1) or 5 V (gain = 2).

Key Features

- High relative accuracy (INL): ±2 LSB maximum at 16 bits

- Low drift 2.5 V reference: 2 ppm/°C typical

- Tiny package: 3 mm × 3 mm, 16-lead LFCSP

- Total unadjusted error (TUE): ±0.1% of FSR maximum

- Offset error: ±1.5 mV maximum